双电源,9-GPIO, 2 acmp, 16 LUTs (max.), 4 CNT/DLY (max.), 8 DFF/LATCH (max.)和其他macrocell

SLG46121为常用的混合信号功能提供了一个小的、低功耗的组件。用户通过编程一次性非易失性存储器(NVM)来配置互连逻辑、I/O引脚和SLG46121的宏单元来创建电路设计。这种高度多功能的设备允许在一个非常小的、低功耗的单集成电路中设计多种混合信号功能。SLG46121上的额外电源(VDD2)提供了在同一设计中连接两个独立电压域的能力。用户可以配置引脚,专用于每个电源,作为输入,输出,或两者(由内部逻辑动态控制)到VDD和VDD2电压域。使用可用的宏单元设计器可以实现混合信号功能桥接两个域或简单地通过水平转换在高到低和低到高的方向。

生命周期状态

宏单元概述

两个模拟比较器;

电压参考(Vref);

五个组合查找表(LUT):

- 一个2比特附近地区;

- 四个3位LUT;

十二组合函数宏单元:

- 四个可选的DFF/锁存器或2位LUT;

- 4个可选择的DFF/Latch或3位LUTs;

- 一个可选择的管道延迟或3位LUT:

- 管道延迟-8级/2输出;

- 一个能带隙;

- 两个可选计数器/延迟或4位LUT;

- 一种可编程延迟/除故障滤波器

一个可选择的管道延迟或3位LUT:

- 管道延迟-8级/2输出;

两个计数器/延迟发生器(CNT/DLY):

- 一个8位计数器/延迟;

- 一个14位计数器/延迟与外部时钟/复位;

八个D触发器/锁存器(DFF)(组合功能宏单元的一部分);

附加逻辑功能- 1个逆变器;

管道延迟- 8级/2输出(组合函数宏单元的一部分);

RC振荡器(RC OSC);

上电复位(POR)。

特性

逻辑与混合信号电路

高度通用的宏细胞

- 1.8 V(±5%)至5 V(±10%)VDD

- V(±5%)to 5v(±10%)VDD2 (VDD2≤VDD)

工作温度范围:-40°C至85°C

符合RoHS要求/不含卤素

Pb-Free

亚博国际官网平台网址

个人计算机和服务器

PC外围设备

消费电子产品

数据通信设备

手持和便携式电子产品

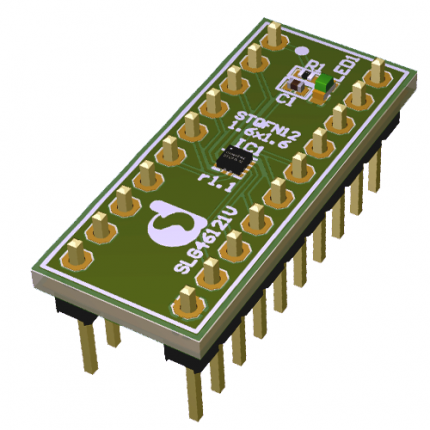

包装和订购

SLG46121V:STQFN-12(1.6 x 1.6 x 0.55毫米,0.4毫米节距)

产品ID后缀表示包样式。

GreenPAK可配置混合信号集成电路简介

GreenPAK Designer软件

GreenPAK开发平台

选择正确的GreenPAK

查看GreenPAK视频的完整列表在我们培训视频库.

该产品可在一个包装:

SLG46121V:STQFN-12(1.6 x 1.6 x 0.55毫米,0.4毫米节距)

开发板选择器

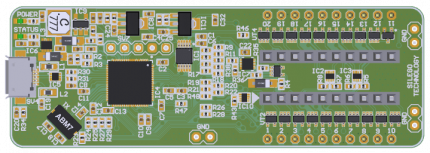

为GreenPAK设备提供完整的编程、仿真和测试功能。用于SLG46xxxX-SKT插座套件。

GreenPAK Advanced Development Board与GreenPAK Designer软件协同工作,允许设计师:

- 在几分钟内程序定制样本

- 在电路中测试GreenPAK项目

- 使用任何GreenPAK设备进行开发

- 程序设计

- 模拟

- 信号和逻辑发生器

- USB接口

- MacOS、Windows和Linux兼容

- 编程与仿真

- 门控扩展集管,用于连接外部测试设备

- 集成信号和逻辑发生器

- 用于视觉指示的LED

完美的面包板和快速原型。

与GreenPAK Designer软件合作,GreenPAK DIP开发委员会允许设计师:

- 在几分钟内程序定制样本

- 在电路中测试GreenPAK项目

- 程序设计

- 模拟

- USB接口

- MacOS、Windows和Linux兼容

- 编程与仿真

- 门控扩展集管,用于连接外部测试设备

格林帕克高级发展委员会

- 程序设计

- 模拟

- 信号和逻辑发生器

GreenPAK DIP发展委员会

完美的面包板和快速原型。

与GreenPAK Designer软件合作,GreenPAK DIP开发委员会允许设计师:

- 在几分钟内程序定制样本

- 在电路中测试GreenPAK项目

- 程序设计

- 模拟

其他组件

双电源可编程混合信号矩阵。VDD = 1.8 V(±5%)至5 V(±10%);VDD2 = 1.8 V(±5%)to VDD。8-GPIO, 2个acmp, 5个LUTs, 11个组合功能Macrocells, 2个CNT/DLYs, 1个PDLY w/ Edge Det.包装:STQFN-12 (1.6 x 1.6 mm)。

价格表:

| 数量 | 1-50 | 51+ |

|---|---|---|

| 价格 | 免费的* | 0.20美元 |

你只付运费

双电源可编程混合信号矩阵。VDD = 1.8 V(±5%)至5 V(±10%);VDD2 = 1.8 V(±5%)to VDD。8-GPIO, 2个acmp, 5个LUTs, 11个组合功能Macrocells, 2个CNT/DLYs, 1个PDLY w/ Edge Det.包装:STQFN-12 (1.6 x 1.6 mm)。

价格表:

| 数量 | 500 - 2999 | 3,000-8,999 | 9000 + |

|---|---|---|---|

| 价格 | 0.20美元 | 0.15美元 | 联系人对话框 |

一个独特的标记将分配给每个程序单元。如果您已经分配了一个PN,请在结帐期间在评论栏中指出它。

包括:SLG4SA12DS-16x16插座适配器,50个SLG46121V样品。

20针DIP原型板*。完美的面包板和快速原型。

*要求GreenPAK DIP适配器(SLG4SA-DIP)与GreenPAK高级开发板一起使用。

GreenPAK高级开发板的GreenPAK DIP适配器。允许将SLG46xxxV DIP原型板与GreenPAK高级开发板一起使用。充当高级开发平台和DIP开发平台之间的桥梁。

格林帕克和格林菲特

三个月前

greenpak最快

邮寄人koen@weijand.nl15分 3答复在一个简单的2bit LUT中,哪个greenpak是最快的?有没有新的、技术更快的环保计划?

背景:尝试在6.78和13.56 Mhz产生一个不重叠的时钟信号。目前使用它为6.78,但差距有点太大

一个月前

我用an-SLG46826G(TSOP-20)在试验板上的SMD适配器上做了一个实验,也就是说,有很多电容性负载。电源电压为3.3V,电路采用2位LUT作为逆变器,一些DFF作为分频器。最大可靠输出切换频率(驱动74LVC2G80)为54 MHz,最大可靠输入频率为62 MHz!相当令人印象深刻。我没有测量传播延迟和电源电流。

如果您的问题是时钟之间的偏差,请尝试添加虚拟LUT以延迟其中一个时钟。

三个月前

你好

谢谢你的帮助。没有特别快的gpak。设备中的所有lut都有大约相同的传播延迟。具体来说,只能作为2位lut使用的块是最快的

问候

Shivani