## DB800 PCI Express Clock Buffer

The SLG74803 is a member of Silego's PCI Express Clock Buffer Family.

#### **Recommended Application:**

PCI Express Gen1, Gen2, and Gen3 Reference Clock Buffer

#### **Output Features:**

- 8 0.7V current-mode differential output pairs

- · Supports zero delay buffer mode and fanout mode

- Bandwidth programming available

#### **Key Specifications:**

- Outputs cycle-cycle jitter < 50ps</li>

- Outputs skew: 50ps

- Phase jitter: PCIe Gen1 < 86ps peak to peak

- Phase jitter: PCIe Gen2 < 3.1ps rms

- Phase jitter: PCIe Gen3 < 1.0ps rms

#### Features/Benefits:

- Spread spectrum modulation tolerant, 0 to -0.5% down spread and +/- 0.25% center spread

- Supports undriven differential outputs in PD# and SRC\_STOP# modes for power management.

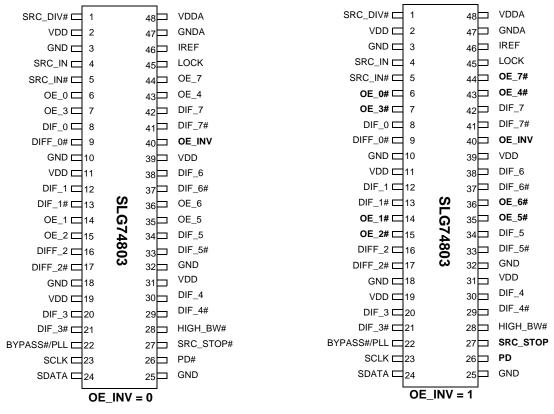

## Pin Configuration

#### 48-pin SSOP & TSSOP

Other brands and names may be claimed as the property of others

## Pin Description for OE\_INV = 0

| Pin # | Name        | Туре | Description                                                                                                                                                                        |

|-------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SRC_DIV#    | IN   | Active low Input for determining SRC output frequency SRC or SRC/2<br>0 = SRC/2, 1 = SRC                                                                                           |

| 2     | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                                                                         |

| 3     | GND         | PWR  | Ground pin.                                                                                                                                                                        |

| 4     | SRC_IN      | IN   | 0.7V Differential SRC TRUE input                                                                                                                                                   |

| 5     | SRC_IN#     | IN   | 0.7V Differential SRC COMPLEMENTARY input                                                                                                                                          |

| 6     | OE_0        | IN   | Active high input for enabling outputs.<br>0 = tri-state outputs, 1 = enable outputs                                                                                               |

| 7     | OE_3        | IN   | Active high input for enabling outputs<br>0 = tri-state outputs, 1 = enable outputs                                                                                                |

| 8     | DIF_0       | OUT  | 0.7V differential true clock outputs                                                                                                                                               |

| 9     | DIF_0#      | OUT  | 0.7V differential complement clock outputs                                                                                                                                         |

| 10    | GND         | PWR  | Ground pin                                                                                                                                                                         |

| 11    | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                                                                         |

| 12    | DIF_1       | OUT  | 0.7V differential true clock outputs                                                                                                                                               |

| 13    | DIF_1#      | OUT  | 0.7V differential complement clock outputs                                                                                                                                         |

| 14    | OE_1        | IN   | Active high input for enabling outputs.<br>0=tri-state outputs, 1=enable outputs                                                                                                   |

| 15    | OE_2        | IN   | Active high input for enabling outputs.<br>0=tri-state outputs, 1=enable outputs                                                                                                   |

| 16    | DIF_2       | OUT  | 0.7V differential true clock outputs                                                                                                                                               |

| 17    | DIF_2#      | OUT  | 0.7V differential complement clock outputs                                                                                                                                         |

| 18    | GND         | PWR  | Ground pin                                                                                                                                                                         |

| 19    | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                                                                         |

| 20    | DIF_3       | OUT  | 0.7V differential true clock outputs                                                                                                                                               |

| 21    | DIF_3#      | OUT  | 0.7V differential complement clock outputs                                                                                                                                         |

| 22    | BYPASS#/PLL | IN   | Input to select Bypass(fan-out) or PLL (ZDB) mode<br>0 = Bypass mode, 1 = PLL mode                                                                                                 |

| 23    | SCLK        | IN   | Clock pin of SMBus circuitry 5V tolerant                                                                                                                                           |

| 24    | SDATA       | I/O  | Data pin for SMBus circuitry 5V tolerant                                                                                                                                           |

| 25    | GND         | PWR  | Ground pin                                                                                                                                                                         |

| 26    | PD#         | IN   | Asynchronous active low input pin, with 120Kohm internal pull-up resistor, used to power down the device. The internal clocks are disabled and the VCO and the crystal are stopped |

| 27    | SRC_STOP    | IN   | Active low input to stop SRC outputs                                                                                                                                               |

| 28    | HIGH_BW#    | IN   | 3.3V input for selecting PLL Band Width<br>0 = High, 1= Low                                                                                                                        |

| 29    | DIF_4#      | OUT  | 0.7V differential complement clock outputs                                                                                                                                         |

| 30    | DIF_4       | OUT  | 0.7V differential true clock outputs                                                                                                                                               |

| 31    | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                                                                         |

## Pin Description for OE\_INV = 0 (continued)

| Pin # | Name   | Туре | Description                                                                                                                                                                                                                           |

|-------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32    | GND    | PWR  | Ground pin.                                                                                                                                                                                                                           |

| 33    | DIF_5# | OUT  | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 34    | DIF_5  | OUT  | 0.7V differential clock outputs                                                                                                                                                                                                       |

| 35    | OE_5   | IN   | Active high inputs for enabling outputs<br>0 = tri-state outputs, 1 = enable outputs                                                                                                                                                  |

| 36    | OE_6   | IN   | Active high input for enabling outputs.<br>0 = tri-state outputs, 1 = enable outputs                                                                                                                                                  |

| 37    | DIF_6# | OUT  | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 38    | DIF_6  | OUT  | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 39    | VDD    | PWR  | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 40    | OE_INV | IN   | This latched input slectes the polarity of the OE pins.<br>0 = OE pins active high, 1 = OE pins active low (OE#)                                                                                                                      |

| 41    | DIF_7# | OUT  | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 42    | DIF_7  | OUT  | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 43    | OE_4   | IN   | Active high input for enabling outputs.<br>0 = tri-state outputs, 1 = enable outputs                                                                                                                                                  |

| 44    | OE_7   | IN   | Active high input for enabling outputs.<br>0 = tri-state outputs, 1 = enable outputs                                                                                                                                                  |

| 45    | LOCK   | OUT  | 3.3V output indicating PLL Lock Status. This pin goes high when lock is achieved                                                                                                                                                      |

| 46    | IREF   | IN   | This pin establishes the reference current for the differential current-mode output pairs. This pin requires a fixed precision resistor tied to ground in order to establish the appropriate current. 475 ohms is the standard value. |

| 47    | GNDA   | PWR  | Ground pin for the PLL core.                                                                                                                                                                                                          |

| 48    | VDDA   | PWR  | 3.3V power for the PLL core.                                                                                                                                                                                                          |

#### Pin Description for OE\_INV = 1

| Pin # | Name        | Туре | Description                                                                                                                |

|-------|-------------|------|----------------------------------------------------------------------------------------------------------------------------|

| 1     | SRC_DIV#    | IN   | Active low Input for determining SRC output frequency SRC or SRC/2<br>0 = SRC/2, 1 = SRC                                   |

| 2     | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                 |

| 3     | GND         | PWR  | Ground pin.                                                                                                                |

| 4     | SRC_IN      | IN   | 0.7V Differential SRC TRUE input                                                                                           |

| 5     | SRC_IN#     | IN   | 0.7V Differential SRC COMPLEMENTARY input                                                                                  |

| 6     | OE_0#       | IN   | Active low input for enabling DIF pair 0<br>1 = tri-state outputs, 0 = enable outputs                                      |

| 7     | OE_3#       | IN   | Active low input for enabling DIF pair 3<br>1 = tri-state outputs, 0 = enable outputs                                      |

| 8     | DIF_0       | OUT  | 0.7V differential true clock outputs                                                                                       |

| 9     | DIF_0#      | OUT  | 0.7V differential complement clock outputs                                                                                 |

| 10    | GND         | PWR  | Ground pin                                                                                                                 |

| 11    | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                 |

| 12    | DIF_1       | OUT  | 0.7V differential true clock outputs                                                                                       |

| 13    | DIF_1#      | OUT  | 0.7V differential complement clock outputs                                                                                 |

| 14    | OE_1#       | IN   | Active low input for enabling DIF pair 1.<br>1=tri-state outputs, 0=enable outputs                                         |

| 15    | OE_2#       | IN   | Active low input for enabling DIF pair 2.<br>1=tri-state outputs, 0=enable outputs                                         |

| 16    | DIF_2       | OUT  | 0.7V differential true clock outputs                                                                                       |

| 17    | DIF_2#      | OUT  | 0.7V differential complement clock outputs                                                                                 |

| 18    | GND         | PWR  | Ground pin                                                                                                                 |

| 19    | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                 |

| 20    | DIF_3       | OUT  | 0.7V differential true clock outputs                                                                                       |

| 21    | DIF_3#      | OUT  | 0.7V differential complement clock outputs                                                                                 |

| 22    | BYPASS#/PLL | IN   | Input to select Bypass(fan-out) or PLL (ZDB) mode<br>0 = Bypass mode, 1 = PLL mode                                         |

| 23    | SCLK        | IN   | Clock pin of SMBus circuitry 5V tolerant                                                                                   |

| 24    | SDATA       | I/O  | Data pin for SMBus circuitry 5V tolerant                                                                                   |

| 25    | GND         | PWR  | Ground pin                                                                                                                 |

| 26    | PD          | IN   | Asynchronous active high input pin used to power down the device. The internal clocks are disabled and the VCO is stopped. |

| 27    | SRC_STOP    | IN   | Active high input to stop SRC outputs                                                                                      |

| 28    | HIGH_BW#    | IN   | 3.3V input for selecting PLL Bandwidth<br>0 = High, 1= Low                                                                 |

| 29    | DIF_4#      | OUT  | 0.7V differential complement clock outputs                                                                                 |

| 30    | DIF_4       | OUT  | 0.7V differential true clock outputs                                                                                       |

| 31    | VDD         | PWR  | Power supply, nominal 3.3V                                                                                                 |

| 32    | GND         | PWR  | Ground pin.                                                                                                                |

| 33    | DIF_5#      | OUT  | 0.7V differential complement clock outputs                                                                                 |

| 34    | DIF_5       | OUT  | 0.7V differential clock outputs                                                                                            |

| 35    | OE_5#       | IN   | Active low input for enabling DIF pair 5.<br>1 = tri-state outputs, 0 = enable outputs                                     |

## SLG74803

| Pin # | Name   | Туре | Description                                                                                                                                                                                                                           |

|-------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36    | OE_6#  | IN   | Active low input for enabling DIF pair 6.<br>1= tri-state outputs, 0= enable outputs                                                                                                                                                  |

| 37    | DIF_6# | OUT  | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 38    | DIF_6  | OUT  | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 39    | VDD    | PWR  | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 40    | OE_INV | IN   | This latched input slectes the polarity of the OE pins.<br>0 = OE pins active high, 1 = OE pins active low (OE#)                                                                                                                      |

| 41    | DIF_7# | OUT  | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 42    | DIF_7  | OUT  | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 43    | OE_4#  | IN   | Active low input for enabling DIF pair 4.<br>1= tri-state outputs, 0 = enable outputs                                                                                                                                                 |

| 44    | OE_7#  | IN   | Active low input for enabling DIF pair 7.<br>1= tri-state outputs, 0 = enable outputs                                                                                                                                                 |

| 45    | LOCK   | OUT  | 3.3V output indicating PLL Lock Status. This pin goes high when lock is achieved                                                                                                                                                      |

| 46    | IREF   | IN   | This pin establishes the reference current for the differential current-mode output pairs. This pin requires a fixed precision resistor tied to ground in order to establish the appropriate current. 475 ohms is the standard value. |

| 47    | GNDA   | PWR  | Ground pin for the PLL core.                                                                                                                                                                                                          |

| 48    | VDDA   | PWR  | 3.3V power for the PLL core.                                                                                                                                                                                                          |

continued

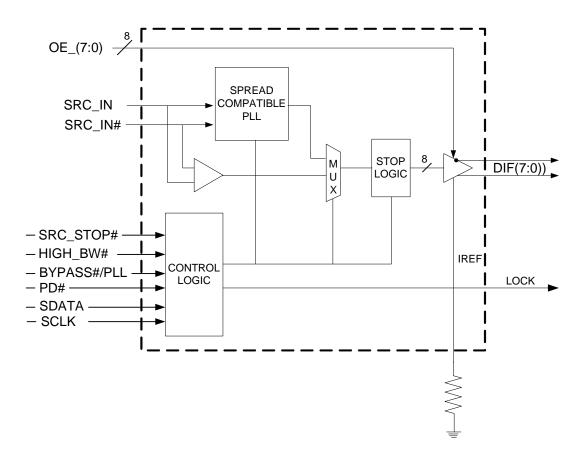

#### **General Description**

The SLG74803 follows the Intel DB800 Differential Buffer Specification v2.0. This buffer provides eight PCI-Express SRC clocks. The SLG74803 is driven by a differential input pair from a CK409/CK410 main clock generator. It provides outputs meeting tight cycle-to-cycle jitter (50ps) and output-to-output skew (50ps) requirements.

## Block Diagram

**Note:** Polarities shown for OE\_INV = 0.

## Absolute Max

| Symbol          | Parameter                                     | Min     | Max                   | Units |

|-----------------|-----------------------------------------------|---------|-----------------------|-------|

| VDD_A           | 3.3V Core Supply Voltage                      |         | 4.6                   | V     |

| VDD_In          | 3.3V Logic Supply Voltage                     |         | 4.6                   | V     |

| V <sub>IL</sub> | Input Low Voltage                             | GND-0.5 |                       | V     |

| V <sub>IH</sub> | Input High Voltage                            |         | V <sub>DD</sub> +0.5V | V     |

| Τ <sub>S</sub>  | Storage Temperature                           | -65     | 150                   | °C    |

| Tambient        | Ambient Operating Temp                        | 0       | 70                    | °C    |

| Tambient        | Ambient Operating Temp<br>(ordering option K) | 0       | 85                    | °C    |

| Tcase           | Case Temperature                              |         | 115                   | °C    |

| ESD protection  | Input ESD protection human<br>body model      | 2000    |                       | V     |

# Electrical Characteristics - Input/Supply/Common Output Parameters $T_A = 0$ to (70°C or 85°C); Supply Voltage $V_{DD} = 3.3V + -5\%$

| Parameter                        | Symbol                | Conditions                                                                                                    | Min                   | Тур | Max                   | Units | Notes |

|----------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|-------|

| Input High Voltage               | V <sub>IH</sub>       | 3.3 V +/-5%                                                                                                   | 2                     |     | V <sub>DD</sub> + 0.3 | V     |       |

| Input Low Voltage                | V <sub>IL</sub>       | 3.3V +/-5%                                                                                                    | GND - 0.3             |     | 0.8                   | V     |       |

| Input High Current               | I <sub>IH</sub>       | $V_{IN} = V_{DD}$ -5 5                                                                                        |                       | uA  |                       |       |       |

| Input Low Current                | I <sub>IL1</sub>      | V <sub>IN</sub> = 0V; Inputs with no pull-up<br>resistors                                                     | -5                    |     |                       | uA    |       |

|                                  | I <sub>IL2</sub>      | V <sub>IN</sub> = 0V; Inputs with pull-up<br>resistors                                                        | -200                  |     |                       | uA    |       |

| Operating Supply Cur-<br>rent    | I <sub>DD3</sub> ,30P | Full Active, CL = Full load;200                                                                               |                       | mA  |                       |       |       |

| Powerdown Current                |                       | All differential pairs driven                                                                                 |                       |     | 70                    | mA    |       |

|                                  | I <sub>DD3,3PD</sub>  | All differential pairs tri-stated                                                                             |                       |     | 4                     | mA    |       |

| Input Frequency <sup>3</sup>     | Fi                    | V <sub>DD</sub> = 3.3V                                                                                        | 50                    |     | 110                   | MHz   | 3     |

| input i requency                 | F <sub>iBYPASS</sub>  | Bypass Mode                                                                                                   | 50                    |     | 400                   | MHz   | 1     |

| Pin Inductance <sup>1</sup>      | L <sub>pin</sub>      |                                                                                                               |                       |     | 7                     | nH    | 1     |

| Input Capacitance <sup>1</sup>   | C <sub>IN</sub>       | Logic Inputs                                                                                                  | 1.5                   |     | 5                     | pF    | 1     |

| input Capacitance                | C <sub>OUT</sub>      | Output pin capacitance                                                                                        | but pin capacitance 6 | pF  | 1                     |       |       |

| PLL Bandwidth                    | BW                    | PLL Bandwidth when<br>PLL_BW#=0                                                                               | 2                     | 3   |                       | MHz   | 1     |

| FLL Bandwidth                    | DVV                   | PLL Bandwidth when<br>PLL_BW#=1                                                                               | 0.7                   | 1   | 1.4                   | MHz   | 1     |

| CLK Stabilization <sup>1,2</sup> | T <sub>STAB</sub>     | From V <sub>DD</sub> Power-Up and after<br>input clock stabilization or<br>deassertion of PD# to 1st<br>clock |                       |     | 1                     | ms    | 1,2   |

| Modulation Frequency             |                       | Triangular Modulation                                                                                         | odulation 30 33 kHz   |     | 1                     |       |       |

| Tdrive_SRC_STOP#                 |                       | DIF output enable after<br>SRC_Stop# de-assertion                                                             |                       |     | 15                    | ns    | 1,3   |

| Tdrive_PD#                       |                       | DIF output enable after PD#<br>de-assertion                                                                   |                       |     | 300                   | us    | 1,3   |

## SLG74803

| Parameter | Symbol | Conditions                        | Min | Тур | Max | Units | Notes |

|-----------|--------|-----------------------------------|-----|-----|-----|-------|-------|

| Tfall     |        | Fall time of PD# and<br>SRC_STOP# |     |     | 5   | ns    | 1     |

| Trise     |        | Rise time of PD# and<br>SRC_STOP# |     |     | 5   | ns    | 2     |

### **Electrical Characteristics - DIF 0.7V Current Mode Differential Pair**

$T_A = 0$  to (70°C or 85°C);  $V_{DD} = 3.3V + -5\%$ ,  $C_L = 2pF$ ,  $R_S = 33.2\Omega$ ,  $R_P = 49.9\Omega$ ,  $I_{REF} = 475\Omega$

| Parameter                          | Symbol                                                                                                                                                                                                                                                                                                | Conditions                                              | Min   | Тур | Max  | Units | Notes |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|-----|------|-------|-------|

| Current Source Output<br>Impedance | Z <sub>O</sub> <sup>1</sup>                                                                                                                                                                                                                                                                           | V <sub>O</sub> = V <sub>X</sub>                         | 3000  |     |      | Ω     | 1     |

| Voltage High                       | VHigh                                                                                                                                                                                                                                                                                                 | Statistical measurement on sin-                         | 660   |     | 850  |       | 1,3   |

| Voltage Low                        | VLow                                                                                                                                                                                                                                                                                                  | gle ended signal using oscillo-<br>scope math function. | -150  |     | 150  | mV    | 1,3   |

| Max Voltage                        | Vovs                                                                                                                                                                                                                                                                                                  | Measurement on single ended                             |       |     | 1150 | mV    | 1     |

| Min Voltage                        | Vuds                                                                                                                                                                                                                                                                                                  | signal using absolute value                             | -300  |     |      |       | 1     |

| Crossing Voltage (abs)             | Vcross(abs)                                                                                                                                                                                                                                                                                           |                                                         | 250   |     | 550  | mB    | 1     |

| Crossing Voltage (var)             | d-Vcross                                                                                                                                                                                                                                                                                              | Variation of crossing over all edges                    |       |     | 140  | mV    | 1     |

| Long Accuracy                      | ppm                                                                                                                                                                                                                                                                                                   | see Tperiod min-max values                              |       |     | 0    | ppm   | 1,2   |

| Rise Time                          | t <sub>r</sub>                                                                                                                                                                                                                                                                                        | V <sub>OL</sub> = 0.175V, VOH = 0.525V                  | 175   |     | 700  | ps    | 1     |

| Fall Time                          | t <sub>f</sub>                                                                                                                                                                                                                                                                                        | V <sub>OH</sub> = 0.525V VOL = 0.175V                   | 175   |     | 700  | ps    | 1     |

| Rise Time Variation                | d-t <sub>r</sub>                                                                                                                                                                                                                                                                                      |                                                         |       |     | 125  | ps    | 1     |

| Fall Time Variation                | d-t <sub>f</sub>                                                                                                                                                                                                                                                                                      |                                                         |       |     | 125  | ps    | 1     |

| Duty Cycle                         | d <sub>t3</sub>                                                                                                                                                                                                                                                                                       | Measurement from differential waveform                  | 45    | 50  | 55   | %     | 1     |

| Skew                               | t <sub>sk3</sub>                                                                                                                                                                                                                                                                                      | V <sub>T</sub> = 50%                                    |       |     | 50   | ps    | 1     |

| littor Cycle to Cycle              | +                                                                                                                                                                                                                                                                                                     | PLL Mode                                                |       | 40  | 50   | ps    | 1,5   |

| Jitter, Cycle to Cycle             | $ \begin{array}{c c c c c c c } \hline \text{ion} & d-t_r & & & & & 125 & \text{ps} \\ \hline \text{on} & d-t_f & & & & 125 & \text{ps} \\ \hline & d_{t3} & & & & & & 125 & \text{ps} \\ \hline & d_{t3} & & & & & & & & & 125 & \text{ps} \\ \hline & d_{t3} & & & & & & & & & & & & & & & & & & &$ | ps                                                      | 1,4,5 |     |      |       |       |

|                                    | t                                                                                                                                                                                                                                                                                                     |                                                         |       | 30  | 86   | ps    | 1,4   |

|                                    | <sup>i</sup> jphasebypass                                                                                                                                                                                                                                                                             | PCIe Gen 2 specs<br>(rms value)                         |       | 2.6 | 3.1  | ps    | 1,4   |

| Jitter, Phase                      |                                                                                                                                                                                                                                                                                                       | PCle Gen 1 specs<br>(pk to pk value)                    |       | 40  | 86   | ps    | 1,6   |

|                                    | t <sub>jphase</sub> PLL                                                                                                                                                                                                                                                                               | PCle Gen 2 specs<br>(rms value)                         |       | 2.8 | 3.1  | ps    | 1,6   |

|                                    |                                                                                                                                                                                                                                                                                                       | PCIe Gen 3 specs<br>(rms value)                         |       | 0.7 | 1.0  | ps    | 1,6,7 |

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that the input clock complies with CK409/CK410/CK505 accuracy requirements.

<sup>3</sup>  $I_{REF} = V_{DD}/(3xR_R)$ . For  $R_R = 475\Omega$  (1%),  $I_{REF} = 2.32mA$ .  $I_{OH} = 6 \times I_{REF}$  and  $V_{OH} = 0.7V @ Z_O = 50\Omega$ <sup>4</sup> Applies to Bypass Mode Only

<sup>5</sup> Measured from differential waveform

<sup>6</sup> Device driven by HP81134A generator

<sup>7</sup> PCIe\* Gen3 filter characteristics are subject to final ratification by PCISIG. Please check the PCI\* SIG for the latest specification.

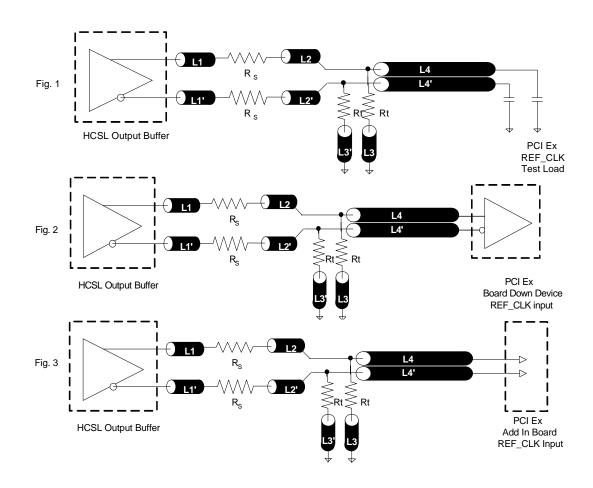

L4 length, Route as coupled stripline 100 ohm

3

| SRC R                                                              | eference              | Clock                    |                      |        |        |

|--------------------------------------------------------------------|-----------------------|--------------------------|----------------------|--------|--------|

| Common Recommendations for Differential Rou                        | Dimension or<br>Value |                          | Unit                 | Figure |        |

| L1 length, Route as non-coupled 50 ohm trac                        | e                     | 0.5 max                  |                      | inch   | 2, 3   |

| L2 length, Route as non-coupled 50 ohm trac                        | e                     | 0.2 max                  |                      | inch   | 2, 3   |

| L3 length, Route as non-coupled 50 ohm trac                        | e                     | 0.2 max                  |                      | inch   | 2, 3   |

| R <sub>S</sub>                                                     |                       | 33                       | ohm                  |        | 2, 3   |

| R <sub>t</sub>                                                     |                       | 49.9                     | ohm                  |        | 2, 3   |

|                                                                    |                       |                          |                      |        |        |

| Down Device Differential Routing                                   |                       | Dimension or Value Unit  |                      | Unit   | Figure |

| L4 length, Route as coupled <b>microstrip</b> 100 ohm differ trace | rential               | 2 min to 16 ma           | 2 min to 16 max inch |        | 2      |

| L4 length, Route as coupled stripline 100 ohm different            | ial trace             | 1.8 min to 14.4 max inch |                      | 2      |        |

| Differential Routing to PCI Express Connector                      | Dime                  | ension or Value          |                      | Unit   | Figure |

| L4 length, Route as coupled <b>microstrip</b> 100 ohm              | -                     | 25 to 14 max             |                      | inch   | 3      |

0.225 min to 12.6 max

inch

#### General SMBus serial interface information for the SLG74803

#### How to Write:

- Controller (host) sends a start bit.

- Controller (host) sends the write address DC (H)

- Silego clock will *acknowledge*

- Controller (host) sends the begining byte location = N

- Silego clock will acknowledge

- Controller (host) sends the data byte count = X

- Silego clock will *acknowledge*

- Controller (host) starts sending Byte N through

- Byte N + X -1

(see Note 2)

- Silego clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

#### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address DC (H)

- Silego clock will *acknowledge*

- Controller (host) sends the begining byte location = N

- Silego clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address DD (H)

- Silego clock will acknowledge

- Silego clock will send the data byte count = X

- Silego clock sends Byte N + X -1

- Silego clock sends Byte 0 through byte X (if  $X_{(H)}$  was written to byte 8).

- Controller (host) will need to acknowledge each byte

- Controllor (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

| Inde          | Index Block Write Operation |          |                             |  |  |  |  |

|---------------|-----------------------------|----------|-----------------------------|--|--|--|--|

| Controller (I | lost)                       |          | Silego(Slave/Receiv-<br>er) |  |  |  |  |

| Т             | Start E                     | Bit      |                             |  |  |  |  |

| Slave Addres  | ss DC (H)                   |          |                             |  |  |  |  |

| WR            | Write                       | ;        |                             |  |  |  |  |

|               | •                           |          | Ack                         |  |  |  |  |

| Beginning E   | Byte = N                    |          |                             |  |  |  |  |

|               |                             |          | Ack                         |  |  |  |  |

| Data Byte C   | ount = X                    |          |                             |  |  |  |  |

|               |                             |          | Ack                         |  |  |  |  |

| Beginning B   | yte N                       |          |                             |  |  |  |  |

|               |                             |          | Ack                         |  |  |  |  |

| 0             |                             | e        |                             |  |  |  |  |

| 0             |                             | X Byte   | 0                           |  |  |  |  |

| 0             |                             | $\times$ | 0                           |  |  |  |  |

|               | Byte N + X - 1              |          | 0                           |  |  |  |  |

| Byte N + X    |                             |          |                             |  |  |  |  |

|               |                             |          | Ack                         |  |  |  |  |

| Р             | Stop E                      | Bit      |                             |  |  |  |  |

|            | Index Block R         | ead C  | Operation            |  |  |  |  |

|------------|-----------------------|--------|----------------------|--|--|--|--|

| Controlle  | er (Host)             | Sil    | ego (Slave/Receiver) |  |  |  |  |

| Т          | Start Bit             |        |                      |  |  |  |  |

| Slave Addr | ess DC (H)            |        |                      |  |  |  |  |

| WR         | Write                 |        |                      |  |  |  |  |

|            |                       |        | Ack                  |  |  |  |  |

| Beginning  | Byte = N              |        |                      |  |  |  |  |

|            |                       |        | Ack                  |  |  |  |  |

| RT         | Repeat Start          |        |                      |  |  |  |  |

| Slave Addr | ess DD <sub>(H)</sub> |        | Ack                  |  |  |  |  |

| RD         | Read                  |        |                      |  |  |  |  |

|            |                       |        | Ack                  |  |  |  |  |

|            |                       |        |                      |  |  |  |  |

|            |                       |        | Data Byte Count = X  |  |  |  |  |

| Ac         | :k                    |        |                      |  |  |  |  |

|            |                       |        | Beginning Byte N     |  |  |  |  |

| Ac         | :k                    |        |                      |  |  |  |  |

|            |                       | e      | 0                    |  |  |  |  |

| C          | )                     | X Byte | 0                    |  |  |  |  |

| C          | )                     | ×      | 0                    |  |  |  |  |

| C          | )                     | ]      |                      |  |  |  |  |

|            |                       |        | Byte N + X - 1       |  |  |  |  |

| N          | Not Ack               |        |                      |  |  |  |  |

| Р          | Stop Bit              |        |                      |  |  |  |  |

## SMBus Table: Frequency Select Register, READ/WRITE ADDRESS (DC/DD)

| Byte 0 | Pin # | Name        | Control Function       | Туре | 0        | 1        | PWD |

|--------|-------|-------------|------------------------|------|----------|----------|-----|

| Bit 7  | -     | PD_Mode     | PD# drive mode         | RW   | driven   | Hi-Z     | 0   |

| Bit 6  | -     | STOP_Mode   | SRC_Stop# drive mode   | RW   | driven   | Hi-Z     | 0   |

| Bit 5  | -     | PD_Polarity | Х                      | RW   | low      | high     | 0   |

| Bit 4  | -     | Reserved    | Reserved               | RW   | Reserved |          | Х   |

| Bit 3  | -     | Reserved    | Reserved               | RW   | Rese     | Reserved |     |

| Bit 2  | -     | PLL_BW#     | Select PLL BW          | RW   | High BW  | Low BW   | 1   |

| Bit 1  | -     | BYPASS#     | BYPASS#/PLL            | RW   | fan-out  | ZDB      | 1   |

| Bit 0  | -     | SRC_DIV#    | SRC Divide by 2 Select | RW   | x/2      | 1x       | 1   |

### SMBus Table:Output Control Register

| Byte 1 | Pin # | Name  | Control Function | Туре | 0       | 1      | PWD |

|--------|-------|-------|------------------|------|---------|--------|-----|

| Bit 7  | 42,41 | DIF_7 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 6  | 38,37 | DIF_6 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 5  | 34,33 | DIF_5 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 4  | 30,29 | DIF_4 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 3  | 20,21 | DIF_3 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 2  | 16,17 | DIF_2 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 1  | 12,13 | DIF_1 | Output Control   | RW   | Disable | Enable | 1   |

| Bit 0  | 8,9   | DIF_0 | Output Control   | RW   | Disable | Enable | 1   |

## SMBus Table:Output Control Register

| Byte 2 |    | Pin # | Name  | Control Function | Туре | 0        | 1         | PWD |

|--------|----|-------|-------|------------------|------|----------|-----------|-----|

| Bit 7  | 42 | 2,41  | DIF_7 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 6  | 38 | 8,37  | DIF_6 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 5  | 34 | 4,33  | DIF_5 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 4  | 30 | 0,29  | DIF_4 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 3  | 20 | 0,21  | DIF_3 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 2  | 10 | 6,17  | DIF_2 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 1  | 12 | 2,13  | DIF_1 | Output Control   | RW   | Free-run | Stoppable | 0   |

| Bit 0  | ł  | 3,9   | DIF_0 | Output Control   | RW   | Free-run | Stoppable | 0   |

## SMBBus Table: Output Control Register

| Byte 3 | Pin # | Name     | Control Function | Туре     | 0          | 1     | PWD |

|--------|-------|----------|------------------|----------|------------|-------|-----|

| Bit 7  |       | Reserved |                  | RW       | Reserved   |       | Х   |

| Bit 6  |       |          | RW               | Reserved |            | Х     |     |

| Bit 5  |       | Reserved |                  | RW       | Reserved   |       | Х   |

| Bit 4  |       | Reserved |                  | RW       | Reserved   |       | Х   |

| Bit 3  |       | Reserved |                  | RW       | Reserved   |       | Х   |

| Bit 2  |       | Reserved |                  | RW       | Rese       | erved | Х   |

| Bit 1  |       | Reserved |                  | RW       | Reserved   |       | Х   |

| Bit 0  |       | Reserved |                  | RW       | N Reserved |       | Х   |

## SMBBus Table: Vendor & Revision ID Register

| Byte 4 | Pin # | Name | Control Function | Туре | 0 | 1 | PWD |

|--------|-------|------|------------------|------|---|---|-----|

| Bit 7  | -     | RID3 |                  | R    | - | - | 0   |

| Bit 6  | -     | RID2 | REVISION ID      | R    | - | - | 0   |

| Bit 5  | -     | RID1 | REVISION ID      | R    | - | - | 0   |

| Bit 4  | -     | RID0 |                  | R    | - | - | 0   |

| Bit 3  | -     | VID3 |                  | R    | - | - | 0   |

| Bit 2  | -     | VID2 | VENDOR ID        | R    | - | - | 1   |

| Bit 1  | -     | VID1 | VENDORID         | R    | - | - | 1   |

| Bit 0  | -     | VID0 |                  | R    | - | - | 0   |

#### SMBus Table: DEVICE ID

| Byte 5 | Pin # | Name              | Control Function | Туре     | 0        | 1 | PWD |

|--------|-------|-------------------|------------------|----------|----------|---|-----|

| Bit 7  | -     | Device ID 7 (MSB) |                  | RW       | Reserved |   | 1   |

| Bit 6  | -     |                   | RW               | Reserved |          | 0 |     |

| Bit 5  | -     |                   | RW               | Reserved |          | 0 |     |

| Bit 4  | -     | Device ID 4       |                  | RW       | Reserved |   | 0   |

| Bit 3  | -     | Device ID 3       |                  | RW       | Reserved |   | 0   |

| Bit 2  | -     | Device ID 2       |                  | RW       | Reserved |   | 0   |

| Bit 1  | -     | Device ID 1       |                  | RW       | Reserved |   | 1   |

| Bit 0  | -     |                   | RW               | Rese     | erved    | 1 |     |

#### SMBus Table: Byte Count Register

| Byte 6 | Pin # | Name | Control Function                                                  | Туре | 0 | 1 | PWD |

|--------|-------|------|-------------------------------------------------------------------|------|---|---|-----|

| Bit 7  | -     | BC7  |                                                                   | RW   | - | - | 0   |

| Bit 6  | -     | BC6  |                                                                   | RW   | - | - | 0   |

| Bit 5  | -     | BC5  |                                                                   | RW   | - | - | 0   |

| Bit 4  | -     | BC4  | Writing to this register con-                                     | RW   | - | - | 0   |

| Bit 3  | -     | BC3  | <ul> <li>figures how many bytes<br/>will be read back.</li> </ul> | RW   | - | - | 0   |

| Bit 2  | -     | BC2  |                                                                   | RW   | - | - | 1   |

| Bit 1  | -     | BC1  |                                                                   | RW   | - | - | 1   |

| Bit 0  | -     | BC0  |                                                                   | RW   | - | - | 1   |

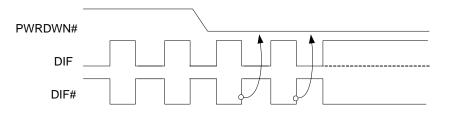

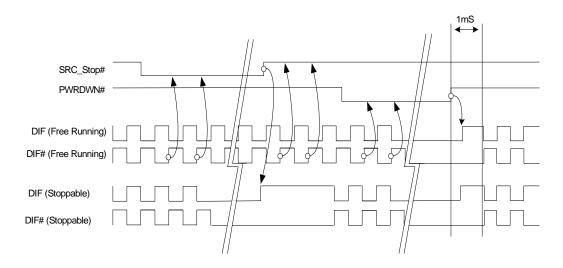

Note: Polarities in timing diagrams are shown OE\_INV = 0. They are similar to OE\_INV = 1.

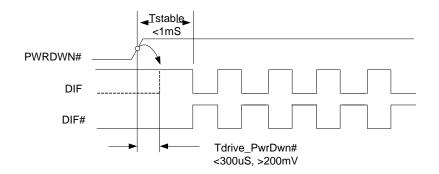

#### PD#, Power Down

The PD# pin cleanly shuts off all clocks and places the device into a power saving mode. PD# must be asserted before shutting off the input clock or power to insure an orderly shutdown. PD is asynchronous active-low input for both powering down the device and powering up the device. When PD# is asserted, all clocks will be driven high, or tri-stated (depending on the PD# drive mode and Output control bits) before the PLL is shut down.

#### **PD# Assertion**

When PD# is sampled low by two consecutive rising edges of DIF#, all DIF outputs must be held High, or tri-stated (depending on the PD# drive mode and Output control bits) on the next High-Low transition of the DIF# outputs. When the PD# drive mode bit is set to '0', all clock outputs will be held with DIF driven High with 2 x I<sub>REF</sub> and DIF# tri-stated. If the PD# drive mode bit is set to '1', both DIF and DIF# are tri-stated.

#### PD# De-assertion

Power-up latency is less than 1 ms. This is the time from de-assertion of the PD# pin, or VDD reaching 3.3V, or the time from valid SRC\_IN clocks until the time that stable clocks are output from the device (PLL Locked). If the PD# drive mode bit is set to '1', all the DIF outputs must driven to a voltage of >200 mV within 300 ms of PD# de-assertion.

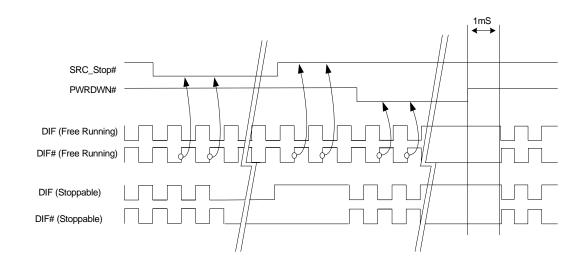

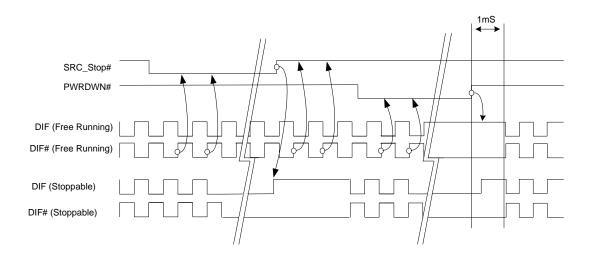

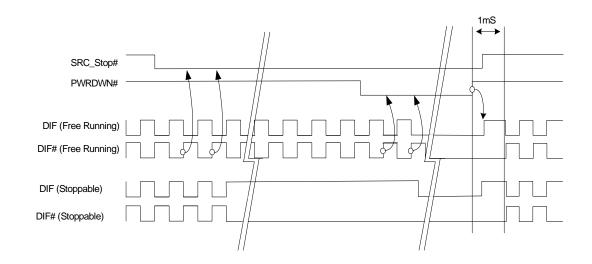

#### SRC\_STOP#

The SRC\_STOP# signal is an active-low asynchronous input that cleanly stops and starts the DIF outputs. A valid clock must be present on SRC\_IN for this input to work properly. The SRC\_STOP# signal is de-bounced and must remain stable for two consecutive rising edges of DIF# to be recognized as a valid assertion or de-assertion.

#### SRC\_STOP# - Assertion

Asserting SRC\_STOP# causes all DIF outputs to stop after their next transition (if the control register settings allow the output to stop). When the SRC\_STOP# drive bit is '0', the final state of all stopped DIF outputs is DIF = High and DIF# = Low. There is no change in output drive current. DIF is driven with  $6xI_{REF}$ . DIF# is not driven, but pulled low by the termination. When the SRC\_STOP# drive bit is '1', the final state of all DIF output pins is Low. Both DIF and DIF# are not driven.

#### SRC\_STOP# - De-assertion (transition from '0' to '1')

All stopped differential outputs resume normal operation in a glitch-free manner. The de-assertion latency to active outputs is 2-6 DIF clock periods, with all DIF outputs resuming simultaneously. If the SRC\_STOP# drive control bit is '1' (tri-state), all stopped DIF outputs must be driven High (>200 mV) within 10 ns of de-assertion.

## SRC\_STOP\_1 (SRC\_Stop = Driven, PD = Driven)

## SRC\_STOP\_2 (SRC\_Stop = Tristate, PD = Driven)

## SRC\_STOP\_3 (SRC\_Stop = Driven, PD = Tristate)

## SRC\_STOP\_4 (SRC\_Stop = Tristate, PD = Tristate)

#### Silego Ordering Information

| Part Number  | Package Type                                | Temperature Range       |

|--------------|---------------------------------------------|-------------------------|

| SLG74803T    | 48 Lead Green Package TSSOP                 | Commerical, 0°C to 70°C |

| SLG74803TTR  | 48 Lead Green Package TSSOP - Tape and Reel | Commerical, 0°C to 70°C |

| SLG74803KT   | 48 Lead Green Package TSSOP                 | Industrial, 0°C to 85°C |

| SLG74803KTTR | 48 Lead Green Package TSSOP - Tape and Reel | Industrial 0°C to 85°C  |

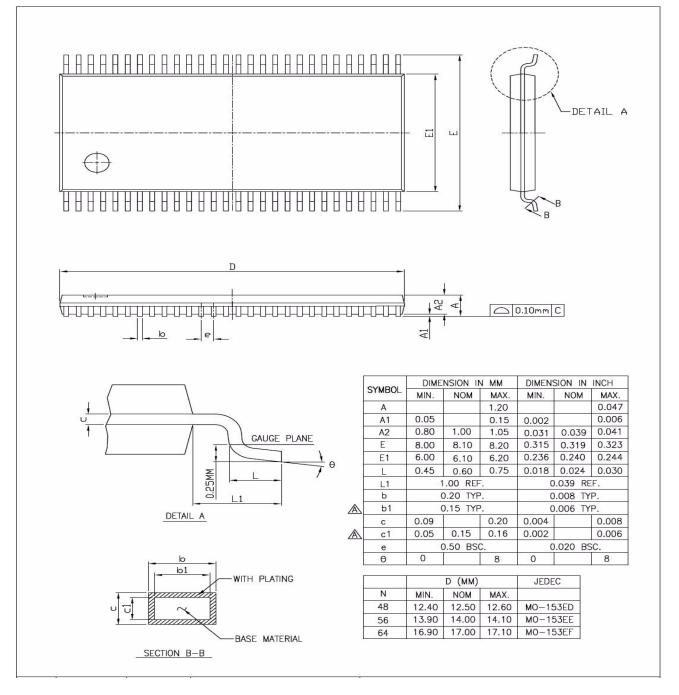

#### Package Drawings and Dimensions

48L TSSOP (6.10 mm body, 0.50 mm pitch) see other dimensions in the table below. (56-pin drawing is shown for reference)

Silego Technology Inc. reserves the right at any time to change specifications and circuitry without notice. Silego Technology Inc. does not assume responsibility for use of circuitry described. Circuit patent licenses are not implied. Silego Technology Inc. products are not authorized for use as critical components in life support devices or systems without obtaining express written approval from the president of Silego Technology Inc. A component is a critical component if failure to perform affects safety, effectiveness, or causes failure of the life support system. These systems are intended for surgical implant into the body, or support or sustain life, or whose failure to perform when properly used can be reasonably expected to result in injury to the user.