# A 22 V, 50 m $\Omega$ , 3 A Reverse Blocking Integrated Power Switch with VIN Lockout Select and MOSFET Current Monitor Output

#### **General Description**

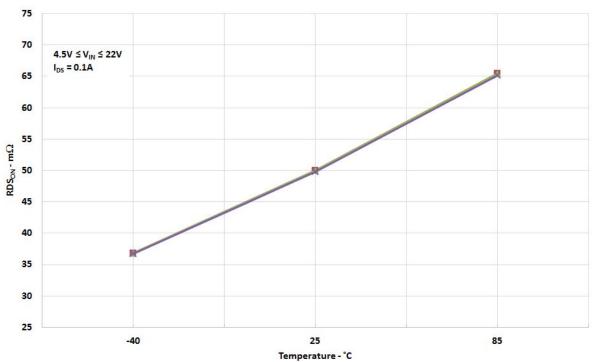

The SLG5NTH1011V is a high-performance, self-powered 50 m $\Omega$  NMOS power switch with back-to-back reverse-current blocking designed for all 4.5 to 22 V power rails up to 3A. Using a proprietary MOSFET design, the SLG5NTH1011V achieves a stable 50 m $\Omega$  RDS<sub>ON</sub> across a wide input/supply voltage range. Using Silego's proprietary CuFET<sup>TM</sup> technology, the SLG5NTH1011V package also exhibits a low thermal resistance for high-current operation.

Designed to operate over a  $-40^{\circ}$ C to  $85^{\circ}$ C range, the SLG5NTH1011V is available in a low thermal resistance, RoHS-compliant, 1.6 x 3.0 mm STQFN package.

#### **Features**

- Wide Operating Supply Voltage: 4.5 V to 22 V

- · Maximum Continuous Switch Current: 3 A

- Back-to-Back FET Reverse Current Blocking, when OFF

- · Internal nFET Power Limiting

- High-performance MOSFET Switch Low RDS<sub>ON</sub>: 50 m $\Omega$  at V<sub>IN</sub> = 22 V Low  $\Delta$ RDS<sub>ON</sub>/ $\Delta$ V<sub>IN</sub>: <0.05 m $\Omega$ /V Low  $\Delta$ RDS<sub>ON</sub>/ $\Delta$ T: <0.06 m $\Omega$ /°C

- 4-Level, Pin-programmable V<sub>IN</sub> Overvoltage Lockout

- · Capacitor-adjustable Inrush Current Control

- Two stage Current Limit Protection:

Resistor-adjustable Active Current Limit

Internal Short-circuit Current limit

- Open Drain FAULT Signaling

- MOSFET Current Analog Output Monitor: 10 μA/A

- · Pb-Free / Halogen-Free / RoHS Compliant Packaging

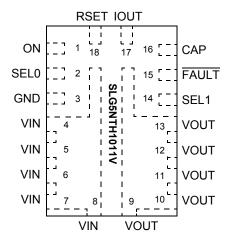

#### **Pin Configuration**

**18-pin STQFN**1.6 x 3.0 mm, 0.40mm pitch

(Top View)

#### **Applications**

- · Power-Rail Switching

- · Multifunction Printers

- · Large-format Copiers

- Telecommunications Equipment

- High-performance Computing

4.5 V and 22 V Point-of-Load Power Distribution

- · Motor Drives

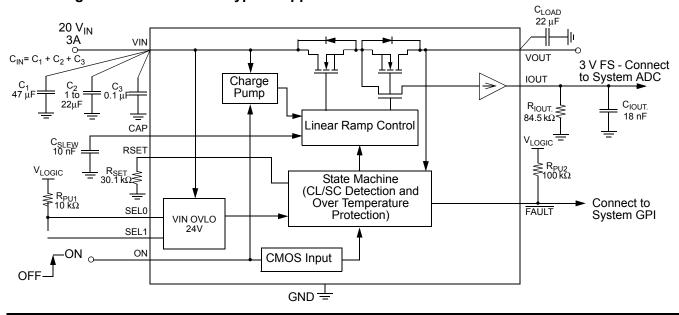

#### Block Diagram and a 20 V / 3 A Typical Application Circuit

### **Pin Description**

| Pin# | Pin Name | Туре   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ON       | Input  | A low-to-high transition on this pin initiates the operation of the SLG5NTH1011V's state machine. ON is an asserted HIGH, level-sensitive CMOS input with $V_{\rm IL} < 0.3$ V and $V_{\rm IH} > 0.85$ V. As the ON pin input circuit does not have an internal pull-down resistor, connect this pin to a general-purpose output (GPO) of a microcontroller, an application processor, or a system controller – do not allow this pin to be open-circuited.                                                                                                               |

| 2    | SEL0     | Input  | As level-sensitive, CMOS inputs with V $_{IL}$ < 0.3 V and V $_{IH}$ > 1.65 V, the SEL0 (LSB) and the SEL1 (MSB) pins select one of four V $_{IN}$ overvoltage lockout thresholds. Please see the Applications Section for additional information and the Electrical Characteristics table for the V $_{IN}$ overvoltage thresholds. A logic LOW on either pin is achieved by connecting the pin of interest to GND; a logic HIGH on either pin is achieved by connecting a 10 k $_{IN}$ 0 external resistor from the pin in question to the system's local logic supply. |

| 3    | GND      | GND    | Pin 3 is the main ground connection for the SLG5NTH1011V's internal charge pump, its gate drive and current-limit circuits as well as its internal state machine. Therefore, use a short, stout connection from Pin 3 to the system's analog or power plane.                                                                                                                                                                                                                                                                                                              |

| 4-8  | VIN      | MOSFET | VIN supplies the power for the operation of the SLG5NTH1011V, its internal control circuitry, and the drain terminal of the back-to-back, reverse-blocking nFET power switch. With 5 pins fused together at VIN, connect a 47 µF (or larger) low-ESR capacitor from this pin to ground. Capacitors used at VIN should be rated at 50 V or higher.                                                                                                                                                                                                                         |

| 9-13 | VOUT     | MOSFET | Drain terminal of n-channel MOSFET (5 pins fused for VOUT). Connect a $22\mu\text{F}$ (or larger) low-ESR capacitor from this pin to ground. Capacitors used at VOUT should be rated at 50 V or higher.                                                                                                                                                                                                                                                                                                                                                                   |

| 14   | SEL1     | Input  | Please see SEL0 Pin Description above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15   | FAULT    | Output | An open drain output, $\overline{FAULT}$ is asserted within $\overline{TFAULT}_{LOW}$ when a $V_{IN}$ overvoltage, a current-limit, or an over-temperature condition is detected. FAULT is deasserted within $\overline{TFAULT}_{HIGH}$ when the fault condition is removed. Connect an 100 k $\Omega$ external resistor from the FAULT pin to local system logic supply.                                                                                                                                                                                                 |

| 16   | CAP      | Output | A low-ESR, stable dielectric, ceramic surface-mount capacitor connected from CAP pin to GND sets the V <sub>OUT</sub> slew rate and overall turn-on time of the SLG5NTH1011V. For best performance, the range for C <sub>SLEW</sub> values are 10 nF $\leq$ C <sub>SLEW</sub> $\leq$ 20 nF $-$ please see typical characteristics for additional information. Capacitors used at the CAP pin should be rated at 10 V or higher. Please consult Applications Section on how to select C <sub>SLEW</sub> based on V <sub>OUT</sub> slew rate and loading conditions.        |

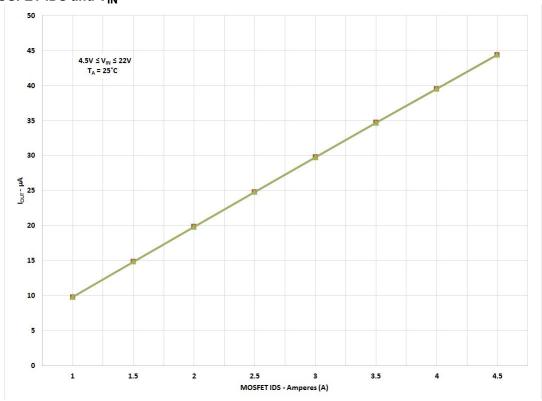

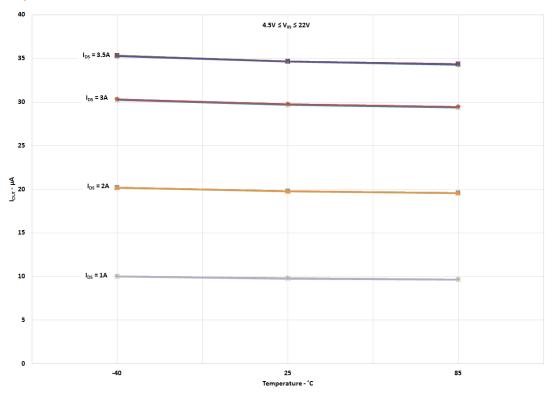

| 17   | IOUT     | Output | IOUT is the SLG5NTH1011V's power MOSFET load current monitor output. As an analog output current, this signal when applied to a ground-reference resistor generates a voltage proportional to the current through the n-channel MOSFET. The $I_{OUT}$ transfer characteristic is typically 10 $\mu$ A/A with a voltage compliance range of 0.5 V $\leq$ V $_{IOUT}$ $\leq$ 4 V. Optimal $I_{OUT}$ linearity is exhibited for 0.5 A $\leq$ $I_{DS}$ $\leq$ 3 A. In addition, it is recommended to bypass the IOUT pin to GND with a 0.18 nF capacitor.                     |

| 18   | RSET     | Input  | A 1%-tolerance, metal-film resistor between 30 k $\Omega$ and 95 k $\Omega$ sets the SLG5NTH1011V's active current limit. A 95 k $\Omega$ resistor sets the SLG5NTH1011V's active current limit to 1 A and a 30 k $\Omega$ resistor sets the active current limit to 3 A.                                                                                                                                                                                                                                                                                                 |

### **Ordering Information**

| Part Number    | Туре                         | Production Flow             |

|----------------|------------------------------|-----------------------------|

| SLG5NTH1011V   | STQFN 18L FC                 | Industrial, -40 °C to 85 °C |

| SLG5NTH1011VTR | STQFN 18L FC (Tape and Reel) | Industrial, -40 °C to 85 °C |

000-005NTH1011-100 Page 2 of 20

### **Absolute Maximum Ratings**

| Parameter                                             | Description                                                  | Conditions                                                                                                              | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                                       |                                                              | Continuous                                                                                                              | -0.3 |      | 30   | V    |

| V <sub>IN</sub> to GND                                | Power Switch Input Voltage to GND                            | Maximum pulsed V <sub>IN</sub> , pulse width <0.1s                                                                      |      |      | 32   | V    |

| V <sub>OUT</sub> to GND                               | Power Switch Output Voltage to GND                           |                                                                                                                         | -0.3 |      | VIN  | V    |

| ON, SEL[1,0], CAP,<br>RSET, IOUT, and<br>FAULT to GND | ON, SEL[1,0], CAP, RSET, IOUT, and FAULT Pin Voltages to GND |                                                                                                                         | -0.3 |      | 7    | V    |

| T <sub>S</sub>                                        | Storage Temperature                                          |                                                                                                                         | -65  |      | 150  | °C   |

| ESD <sub>HBM</sub>                                    | ESD Protection                                               | Human Body Model                                                                                                        | 2000 |      |      | V    |

| ESD <sub>CDM</sub>                                    | ESD Protection                                               | Charged Device Model                                                                                                    | 500  |      |      | V    |

| MSL                                                   | Moisture Sensitivity Level                                   |                                                                                                                         |      | 1    |      |      |

| $\theta_{JA}$                                         | Thermal Resistance                                           | 1.6 x 3.0 mm 18L STQFN; Determined with the device mounted onto a 1 in <sup>2</sup> , 1 oz. copper pad of FR-4 material |      | 40   |      | °C/W |

| $T_{J,MAX}$                                           | Maximum Junction Temperature                                 |                                                                                                                         |      | 150  |      | °C   |

| MOSFET IDS <sub>CONT</sub>                            | Continuous Current from VIN to VOUT                          | T <sub>J</sub> < 150°C                                                                                                  |      |      | 4    | Α    |

| MOSFET IDS <sub>PEAK</sub>                            | Peak Current from VIN to VOUT                                | Maximum pulsed switch current,<br>pulse width < 1 ms, 1% duty cy-<br>cle                                                |      |      | 5    | А    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Electrical Characteristics**

$4.5~\text{V} \leq \text{V}_{\text{IN}} \leq 22~\text{V};~C_{\text{IN}} = 47~\mu\text{F},~T_{\text{A}} = -40^{\circ}\text{C}~\text{to}~85^{\circ}\text{C},~\text{unless otherwise noted}.~\text{Typical values are at}~T_{\text{A}} = 25^{\circ}\text{C}$

| Parameter                 | Description                                       | Conditions                                        | Min. | Тур. | Max. | Unit |

|---------------------------|---------------------------------------------------|---------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>           | Operating Input Voltage                           |                                                   | 4.5  |      | 22   | V    |

| V <sub>IN(OVLO)</sub>     |                                                   | V <sub>IN</sub> ↑; SEL[1,0] = [0,0]               | 5.6  | 6    | 6.3  | V    |

|                           | V <sub>IN</sub> Overvoltage Lockout Threshold     | V <sub>IN</sub> ↑; SEL[1,0] = [0,1]               | 10.2 | 10.8 | 11.4 | V    |

|                           | VIN Overvoitage Lockout Threshold                 | V <sub>IN</sub> ↑; SEL[1,0] = [1,0]               | 13.5 | 14.4 | 15.2 | V    |

|                           |                                                   | V <sub>IN</sub> ↑; SEL[1,0] = [1,1]               | 22.6 | 24   | 25.2 | V    |

| V <sub>IN(OVLOHYST)</sub> | V <sub>IN</sub> Overvoltage Lockout<br>Hysteresis |                                                   |      | 2    |      | %    |

| V <sub>IN(UVLO)</sub>     | V <sub>IN</sub> Undervoltage Lockout<br>Threshold | V <sub>IN</sub> ↓                                 | 3    | 3.2  | 3.4  | V    |

| IQ                        | Quiescent Supply Current                          | ON = HIGH;<br>I <sub>DS</sub> = 0 A               |      | 0.5  | 0.6  | mA   |

| I <sub>SHDN</sub>         | OFF Mode Supply Current                           | ON = LOW;<br>I <sub>DS</sub> = 0 A                |      | 1    | 3    | μΑ   |

| RDS <sub>ON</sub>         | ON Resistance                                     | T <sub>A</sub> = 25°C;<br>I <sub>DS</sub> = 0.1 A |      | 50   | 52   | mΩ   |

| IND30N                    | ON NESISTANCE                                     | T <sub>A</sub> = 85°C;<br>I <sub>DS</sub> = 0.1 A |      | 65   | 68   | mΩ   |

000-005NTH1011-100 Page 3 of 20

#### **Electrical Characteristics** (continued)

$4.5 \text{ V} \le \text{V}_{\text{IN}} \le 22 \text{ V}; \text{C}_{\text{IN}} = 47 \text{ }\mu\text{F}, \text{T}_{\text{A}} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } \text{T}_{\text{A}} = 25 ^{\circ}\text{C}$

| Parameter                | Description                                                     | Conditions                                                                                                                                                      | Min.                              | Тур.     | Max.              | Unit |

|--------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|-------------------|------|

| MOSFET<br>IDS            | Current from VIN to VOUT                                        | Continuous                                                                                                                                                      |                                   |          | 3                 | Α    |

| I <sub>REVERSE</sub>     | MOSFET Reverse-Leakage Current                                  | V <sub>IN</sub> = 0 V; V <sub>OUT</sub> = 22 V; ON = 0 V                                                                                                        |                                   |          | 3                 | μA   |

|                          | Active Current Limit, I <sub>ACL</sub>                          | $V_{OUT} > 0.5 \text{ V; R}_{SET} = 30.1 \text{ k}\Omega$                                                                                                       | 3                                 | 3.2      | 3.4               | Α    |

| I <sub>LIMIT</sub>       | Short-circuit Current Limit, I <sub>SCL</sub>                   | V <sub>OUT</sub> < 0.5 V                                                                                                                                        |                                   |          |                   | Α    |

| T <sub>ACL</sub>         | Active Current Limit Response Time                              | $R_{SET}$ = 51.6 kΩ                                                                                                                                             |                                   | 120      |                   | μs   |

|                          | MOSFET Current Analog Monitor Out-                              | I <sub>LOAD</sub> = 1 A                                                                                                                                         | 9.3                               | 10       | 10.7              | μA   |

| I <sub>OUT</sub>         | put                                                             | I <sub>LOAD</sub> = 3 A                                                                                                                                         | 28.5                              | 30       | 31.5              | μA   |

| T <sub>IOUT</sub>        | I <sub>OUT</sub> Response Time to Change in Main MOSFET Current | C <sub>IOUT</sub> = 180 pF;<br>Step load 0 to 2.4 A; 0% to 90% I <sub>OUT</sub>                                                                                 |                                   | 45       |                   | μs   |

| C <sub>LOAD</sub>        | Output Load Capacitance                                         | C <sub>LOAD</sub> connected from VOUT to GND                                                                                                                    |                                   | 22       |                   | μF   |

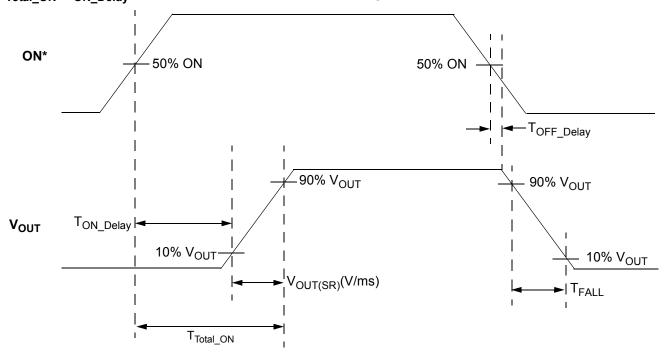

| т                        | ON Delay Time                                                   | 50% ON to 10% $V_{OUT}$ ↑;<br>$V_{IN}$ = 4.5 V; $C_{SLEW}$ = 10 nF;<br>$R_{LOAD}$ = 100 $\Omega$ , $C_{LOAD}$ = 10 $\mu$ F                                      |                                   | 0.3      | 0.5               | ms   |

| T <sub>ON_Delay</sub>    | ON Delay Time                                                   | 50% ON to 10% $V_{OUT} \uparrow$ ;<br>$V_{IN}$ = 22 V; $C_{SLEW}$ = 10 nF;<br>$R_{LOAD}$ = 100 $\Omega$ , $C_{LOAD}$ = 10 $\mu$ F                               |                                   | 0.7      | 1.2               | ms   |

|                          |                                                                 | 50% ON to 90% V <sub>OUT</sub> ↑                                                                                                                                | Set by                            | External | C <sub>SLEW</sub> | ms   |

| T <sub>Total_ON</sub>    | Total Turn-on Time                                              | 50% ON to 90% $V_{OUT}$ ↑; $V_{IN}$ = 4.5 V; $C_{SLEW}$ = 10 nF; Time $R_{LOAD}$ = 100 $\Omega$ , $C_{LOAD}$ = 10 $\mu$ F                                       |                                   | 1.5      | 2.1               | ms   |

| _                        |                                                                 | 50% ON to 90% $V_{OUT} \uparrow$ ;<br>$V_{IN}$ = 22 V; $C_{SLEW}$ = 10 nF;<br>$R_{LOAD}$ = 100 $\Omega$ , $C_{LOAD}$ = 10 $\mu$ F                               |                                   | 6.5      | 8                 | ms   |

|                          |                                                                 | 50% ON to 90% V <sub>OUT</sub> ↑                                                                                                                                | Set by External C <sub>SLEW</sub> |          |                   | V/ms |

| V <sub>OUT(SR)</sub>     | V <sub>OUT</sub> Slew rate                                      | 10% to 90% $V_{OUT}$ ↑;<br>$V_{IN}$ = 4.5 to 22 V; $C_{SLEW}$ = 10 nF;<br>$R_{LOAD}$ = 100 Ω, $C_{LOAD}$ = 10 μF                                                | 2.7                               | 3.2      | 3.9               | V/ms |

| T <sub>OFF_Delay</sub>   | OFF Delay Time                                                  | 50% ON to $V_{OUT} \downarrow$ ;<br>R <sub>LOAD</sub> = 100 Ω, No C <sub>LOAD</sub>                                                                             |                                   | 15       |                   | μs   |

| T <sub>FALL</sub>        | V <sub>OUT</sub> Fall Time                                      | 90% $V_{OUT}$ to 10% $V_{OUT} \downarrow$ ;<br>ON = HIGH-to-LOW;<br>$V_{IN}$ = 4.5 V to 22 V;<br>$R_{LOAD}$ = 100 $\Omega$ , No $C_{LOAD}$                      | 10.4                              | 12.7     | 14.3              | μs   |

| TFAULT <sub>LOW</sub>    | FAULT Assertion Time                                            | Abnormal Step Load Current event to $\overline{FAULT}\downarrow$ ; $I_{ACL}$ = 1 A; $V_{IN}$ = 22 V; $R_{SET}$ = 95 k $\Omega$ ; switch in 20 $\Omega$ load     |                                   | 80       |                   | μs   |

| TFAULT <sub>HIGH</sub>   | FAULT De-assertion Time                                         | Delay to $\overline{FAULT}\uparrow$ after fault condition is removed; $I_{ACL}$ = 1 A; $V_{IN}$ = 22 V; $R_{SET}$ = 95 k $\Omega$ ; switch out 20 $\Omega$ load |                                   | 180      |                   | μs   |

| FAULT <sub>VOL</sub>     | FAULT Output Low Voltage                                        | I <sub>FAULT</sub> = 1 mA                                                                                                                                       |                                   | 0.2      |                   | V    |

| ON_V <sub>IH</sub>       | ON Pin Input High Voltage                                       |                                                                                                                                                                 | 0.9                               |          | 5                 | V    |

| ON_V <sub>IL</sub>       | ON Pin Input Low Voltage                                        |                                                                                                                                                                 | -0.3                              | 0        | 0.3               | V    |

| SEL[1,0]_V <sub>IH</sub> | SEL[1,0] pins Input High Voltage                                |                                                                                                                                                                 | 1.65                              |          | 4.5               | V    |

000-005NTH1011-100 Page 4 of 20

#### **Electrical Characteristics** (continued)

$4.5 \text{ V} \le \text{V}_{\text{IN}} \le 22 \text{ V}$ ;  $C_{\text{IN}} = 47 \, \mu\text{F}$ ,  $T_{\text{A}} = -40 \, ^{\circ}\text{C}$  to  $85 \, ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_{\text{A}} = 25 \, ^{\circ}\text{C}$

| Parameter                | Description                           | Conditions               | Min. | Тур. | Max. | Unit |

|--------------------------|---------------------------------------|--------------------------|------|------|------|------|

| SEL[1,0]_V <sub>IL</sub> | SEL[1,0] pins Input Low Voltage       |                          | -0.3 |      | 0.3  | V    |

| I <sub>ON(Leakage)</sub> | ON Pin Leakage Current                | 1V ≤ ON ≤ 5V or ON = GND |      |      | 1    | μA   |

| THERMON                  | Thermal Protection Shutdown Threshold |                          |      | 125  |      | °C   |

| THERM <sub>OFF</sub>     | Thermal Protection Restart Threshold  |                          |      | 100  |      | °C   |

| Notos:                   | •                                     | <del></del>              |      |      |      | •    |

#### Notes:

### T<sub>Total ON</sub>, T<sub>ON Delay</sub> and Slew Rate Measurement Timing Details

<sup>\*</sup> Rise and Fall times of the ON signal are 100 ns

000-005NTH1011-100 Page 5 of 20

<sup>1.</sup> Refer to typical Timing Parameter vs.  $C_{SLEW}$  performance charts for additional information when available.

### **Typical Performance Characteristics**

### $\ensuremath{\mathsf{RDS_{ON}}}$ vs. Temperature and $\ensuremath{\mathsf{V_{IN}}}$

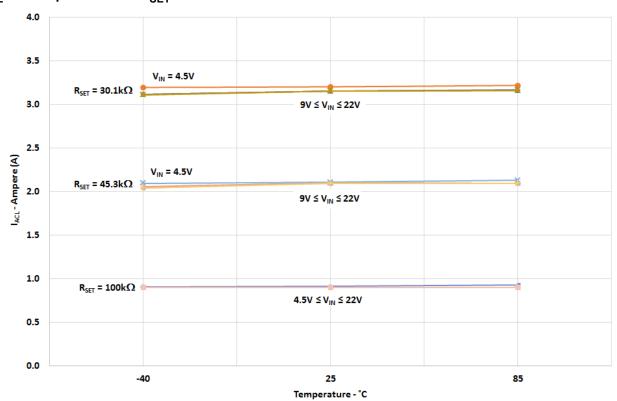

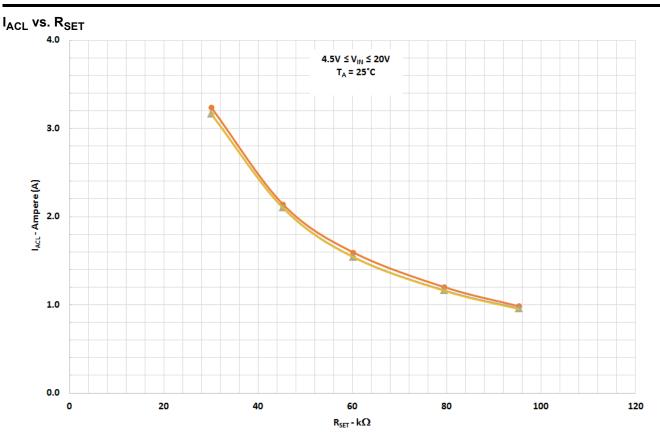

$I_{ACL}$  vs. Temperature and  $R_{SET}$

000-005NTH1011-100 Page 6 of 20

### $I_{OUT}$ vs. MOSFET IDS and $V_{IN}$

000-005NTH1011-100 Page 7 of 20

$I_{OUT}$  vs. Temperature and MOSFET IDS

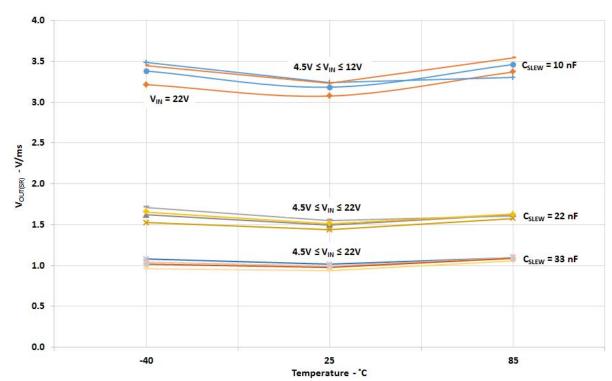

### $\mathbf{V}_{\text{OUT}}$ Slew Rate vs. Temperature, $\mathbf{V}_{\text{IN}},$ and $\mathbf{C}_{\text{SLEW}}$

000-005NTH1011-100 Page 8 of 20

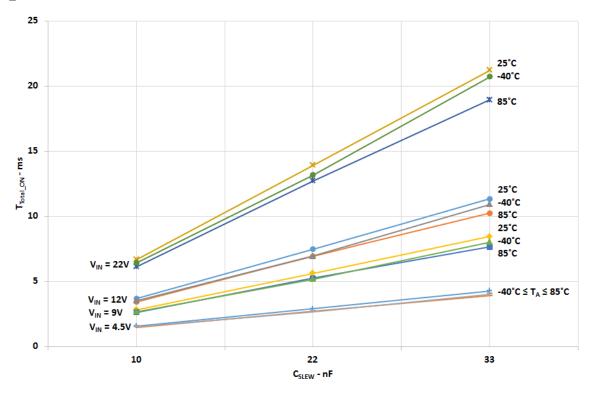

## $\rm T_{Total\_ON}$ vs. $\rm C_{SLEW}, \, \rm V_{IN}, \, and \, Temperature$

000-005NTH1011-100 Page 9 of 20

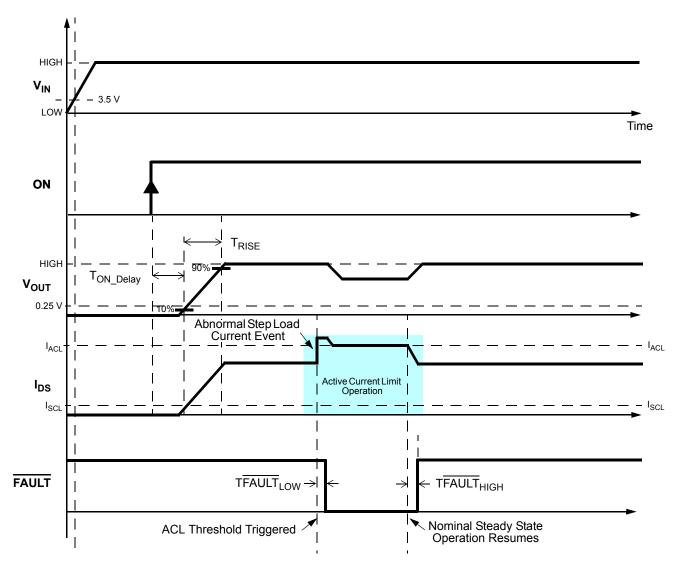

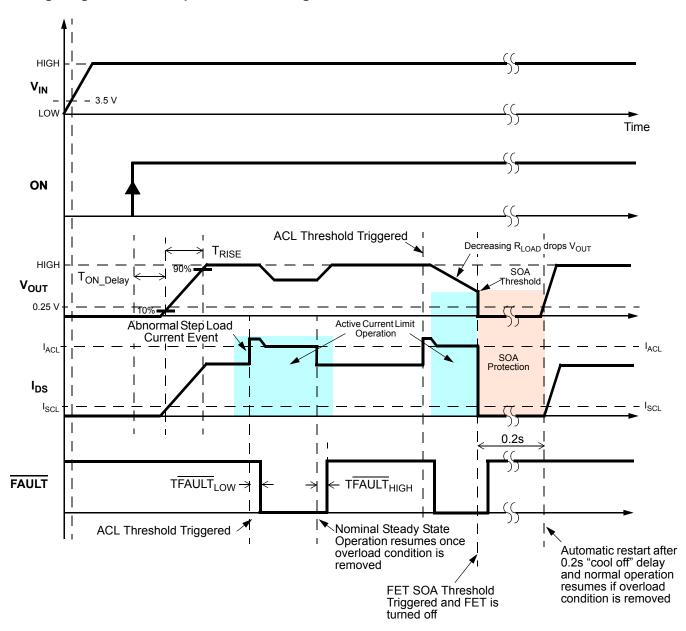

### **Timing Diagram - Basic Operation including Active Current Limit Protection**

000-005NTH1011-100 Page 10 of 20

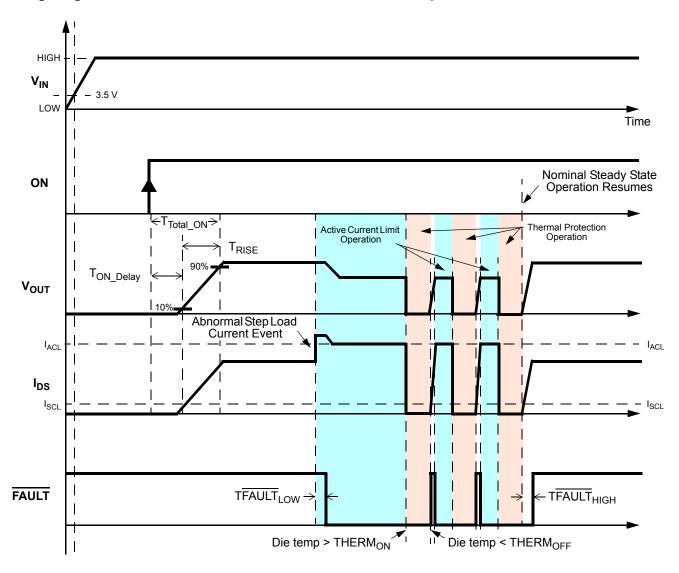

### **Timing Diagram - Active Current Limit & Thermal Protection Operation**

000-005NTH1011-100 Page 11 of 20

### Timing Diagram - Basic Operation including Active Current + Internal FET SOA Protection

000-005NTH1011-100 Page 12 of 20

#### **Applications Information**

#### **HFET1 Safe Operating Area Explained**

Silego's HFET1 integrated power controllers incorporate a number of internal protection features that prevents them from damaging themselves or any other circuit or subcircuit downstream of them. One particular protection feature is their Safe Operation Area (SOA) protection. SOA protection is automatically activated under overpower and, in some cases, under overcurrent conditions. Overpower SOA is activated if package power dissipation exceeds an internal 5W threshold longer than 2.5 ms. HFET1 devices will quickly switch off (open circuit) upon overpower detection and automatically resume (close) nominal operation once overpower condition no longer exists.

One possible way to have an overpower condition trigger SOA protection is when HFET1 products are enabled into heavy output resistive loads and/or into large load capacitors. It is under these conditions to follow carefully the "Safe Start-up Loading" guidance in the Applications section of the datasheet. During an overcurrent condition, HFET1 devices will try to limit the output current to the level set by the external  $R_{\text{SET}}$  resistor. Limiting the output current, however, causes an increased voltage drop across the FET's channel because the FET's RDS<sub>ON</sub> increased as well. Since the FET's RDS<sub>ON</sub> is larger, package power dissipation also increases. If the resultant increase in package power dissipation is higher/equal than 5 W for longer than 2.5 ms, internal SOA protection will be triggered and the FET will open circuit (switch off). Every time SOA protection is triggered, all HFET1 devices will automatically attempt to resume nominal operation after 160 ms.

#### Safe Start-up Condition

SLG5NTH1011V has built-in protection to prevent over-heating during start-up into a heavy load. Overloading the VOUT pin with a capacitor and a resistor may result in non-monotonic  $V_{OUT}$  ramping. In general, under light loading on  $V_{OUT}$ ,  $V_{OUT}$  ramping can be controlled with  $C_{SLEW}$  value. The following equation serves as a guide:

$$C_{SLEW} = \frac{T_{RISE}}{V_{IN}} \times 5 \,\mu\text{A} \times \frac{20}{3}$$

where

$T_{RISE}$  = Total rise time from 10%  $V_{OUT}$  to 90%  $V_{OUT}$

V<sub>IN</sub> = Input Voltage

C<sub>SI FW</sub> = Capacitor value for CAP pin

When capacitor and resistor loading on  $V_{OUT}$  during start up, the following tables will ensure  $V_{OUT}$  ramping is monotonic without triggering internal protection:

| Safe Start-up Loading for V <sub>IN</sub> = 22 V (Monotonic Ramp) |                                     |                        |                         |  |  |  |  |  |

|-------------------------------------------------------------------|-------------------------------------|------------------------|-------------------------|--|--|--|--|--|

| Slew Rate (V/ms)                                                  | C <sub>SLEW</sub> (nF) <sup>3</sup> | C <sub>LOAD</sub> (μF) | $R_{LOAD}$ ( $\Omega$ ) |  |  |  |  |  |

| 0.5                                                               | 66.7                                | 500                    | 80                      |  |  |  |  |  |

| 1.0                                                               | 33.3                                | 250                    | 80                      |  |  |  |  |  |

| 1.5                                                               | 22.2                                | 160                    | 80                      |  |  |  |  |  |

| 2.0                                                               | 16.7                                | 120                    | 80                      |  |  |  |  |  |

| 2.5                                                               | 13.3                                | 100                    | 80                      |  |  |  |  |  |

000-005NTH1011-100 Page 13 of 20

| Safe Start-up Loading for V <sub>IN</sub> = 12 V (Monotonic Ramp) |                                     |                        |                               |  |  |  |  |  |

|-------------------------------------------------------------------|-------------------------------------|------------------------|-------------------------------|--|--|--|--|--|

| Slew Rate (V/ms)                                                  | C <sub>SLEW</sub> (nF) <sup>3</sup> | C <sub>LOAD</sub> (μF) | $R_{LOAD}\left(\Omega\right)$ |  |  |  |  |  |

| 1                                                                 | 33.3                                | 500                    | 20                            |  |  |  |  |  |

| 2                                                                 | 16.7                                | 250                    | 20                            |  |  |  |  |  |

| 3                                                                 | 11.1                                | 160                    | 20                            |  |  |  |  |  |

| 4                                                                 | 8.3                                 | 120                    | 20                            |  |  |  |  |  |

| 5                                                                 | 6.7                                 | 100                    | 20                            |  |  |  |  |  |

Note 3: Select the closest-value tolerance capacitor.

#### Setting the SLG5NTH1011V's Active Current Limit

| R <sub>SET</sub> (kΩ) | Active Current Limit (A) <sup>4</sup> |

|-----------------------|---------------------------------------|

| 95                    | 1                                     |

| 45                    | 2                                     |

| 30                    | 3                                     |

Note 4: Active Current Limit accuracy is ±15% over voltage range and over temperature range.

#### Setting the SLG5NTH1011V's Input Overvoltage Lockout Threshold

As shown in the table below, SEL[1,0] selects the  $V_{IN}$  overvoltage threshold at which the SLG5NTH1011V's internal state machine will turn OFF (open circuit) the power MOSFET if  $V_{IN}$  exceeds the selected threshold.

| SEL1 | SEL0 | V <sub>IN(OVLO)</sub> (Typ) |

|------|------|-----------------------------|

| 0    | 0    | 6                           |

| 0    | 1    | 10.8                        |

| 1    | 0    | 14.4                        |

| 1    | 1    | 24                          |

For example, SEL[1,1] would be the most appropriate setting for applications where the steady-state  $V_{IN}$  can extend up to 20V without causing any damage to the SLG5NTH1011V since the IC is 29-V tolerant.

With an activated SLG5NTH1011V (ON=HIGH) and at any time  $V_{IN}$  crosses the programmed  $V_{IN}$  overvoltage threshold, the state machine opens the power switch and asserts the FAULT pin within TFAULT LOW.

In applications with a deactivated or inactive SLG5NTH1011V ( $V_{IN} > V_{IN(OVLO)}$  and ON=LOW) and if the applied  $V_{IN}$  is higher than the programmed  $V_{IN(OVLO)}$  threshold, the SLG5NTH1011V's state machine will keep the power switch open circuited if the ON pin is toggled LOW-to-HIGH. In these cases, the FAULT pin will also be asserted within TFAULT and will remain asserted until VIN resumes nominal, steady-state operation.

In all cases, the SLG5NTH1011V's  $V_{IN}$  undervoltage lockout threshold is fixed at  $V_{IN(UVLO)}$ .

000-005NTH1011-100 Page 14 of 20

#### **Power Dissipation**

The junction temperature of the SLG5NTH1011V depends on different factors such as board layout, ambient temperature, and other environmental factors. The primary contributor to the increase in the junction temperature of the SLG5NTH1011V is the power dissipation of its power MOSFET. Its power dissipation and the junction temperature in nominal operating mode can be calculated using the following equations:

$$PD = RDS_{ON} \times I_{DS}^{2}$$

where:

PD = Power dissipation, in Watts (W) RDS $_{ON}$  = Power MOSFET ON resistance, in Ohms ( $\Omega$ )  $I_{DS}$  = Output current, in Amps (A) and

$$T_J = PD \times \theta_{JA} + T_A$$

where:

$T_J$  = Junction temperature, in Celsius degrees (°C)  $\theta_{JA}$  = Package thermal resistance, in Celsius degrees per Watt (°C/W)  $T_A$  = Ambient temperature, in Celsius degrees (°C)

In current-limit mode, the SLG5NTH1011V's power dissipation can be calculated by taking into account the voltage drop across the power switch ( $V_{IN}$ - $V_{OUT}$ ) and the magnitude of the output current in current-limit mode ( $I_{ACL}$ ):

PD =

$$(V_{IN}-V_{OUT}) \times I_{ACL}$$

or

PD =  $(V_{IN} - (R_{LOAD} \times I_{ACL})) \times I_{ACL}$

where:

PD = Power dissipation, in Watts (W)  $V_{IN}$  = Input Voltage, in Volts (V)  $R_{LOAD}$  = Load Resistance, in Ohms ( $\Omega$ )  $I_{ACL}$  = Output limited current, in Amps (A)  $V_{OUT}$  =  $R_{LOAD}$  x  $I_{ACL}$

000-005NTH1011-100 Page 15 of 20

### **Package Top Marking System Definition**

1011V - Part ID Field WW - Date Code Field<sup>1</sup> NNN - Lot Traceability Code Field<sup>1</sup> A - Assembly Site Code Field<sup>2</sup> RR - Part Revision Code Field<sup>2</sup>

Note 1: Each character in code field can be alphanumeric A-Z and 0-9

Note 2: Character in code field can be alphabetic A-Z

000-005NTH1011-100 Page 16 of 20

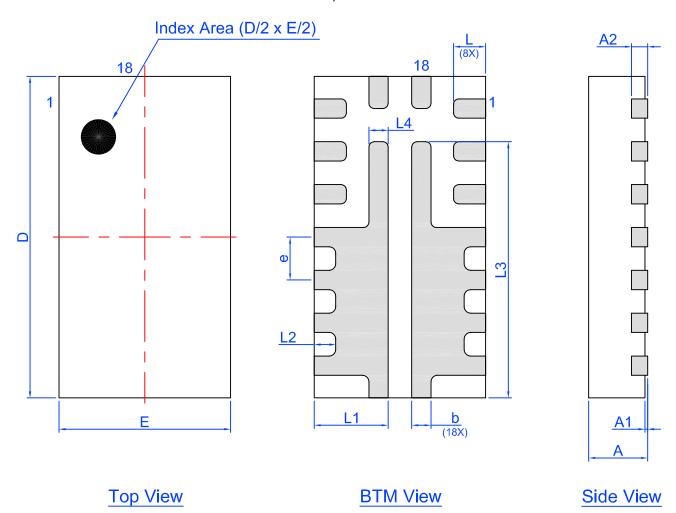

### **Package Drawing and Dimensions**

# 18 Lead TQFN Package 1.6 x 3 mm (Fused Lead) JEDEC MO-220, Variation WCEE

### Unit: mm

| Symbol | Min   | Nom.     | Max  | Symbol | Min  | Nom. | Max  |

|--------|-------|----------|------|--------|------|------|------|

| Α      | 0.50  | 0.55     | 0.60 | D      | 2.95 | 3.00 | 3.05 |

| A1     | 0.005 | -        | 0.05 | E      | 1.55 | 1.60 | 1.65 |

| A2     | 0.10  | 0.15     | 0.20 | L      | 0.25 | 0.30 | 0.35 |

| b      | 0.13  | 0.18     | 0.23 | L1     | 0.64 | 0.69 | 0.74 |

| е      | (     | 0.40 BSC | ,    | L2     | 0.15 | 0.20 | 0.25 |

| L3     | 2.34  | 2.39     | 2.44 | L4     | 0.13 | 0.18 | 0.23 |

000-005NTH1011-100 Page 17 of 20

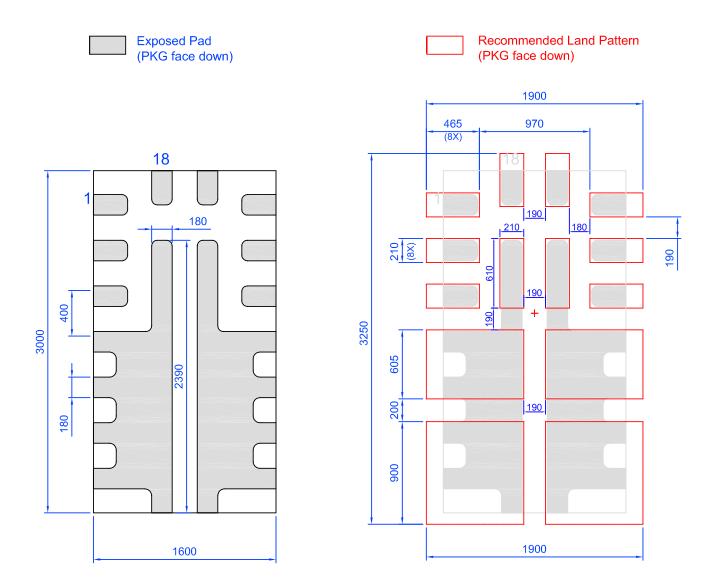

### SLG5NTH1011V 18-pin STQFN PCB Landing Pattern

Note: All dimensions shown in micrometers (µm)

000-005NTH1011-100 Page 18 of 20

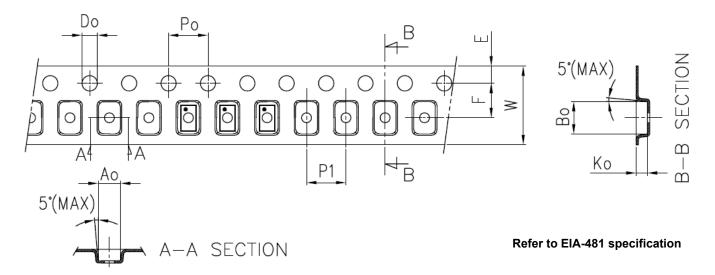

#### Tape and Reel Specifications

| Dookogo                       | # of         | Nominal              | Max      | Units   | Reel &           | Leade   | r (min)        | Trailer | (min)          | Tape          | Part          |

|-------------------------------|--------------|----------------------|----------|---------|------------------|---------|----------------|---------|----------------|---------------|---------------|

| Package<br>Type               | # OI<br>Pins | Package Size<br>[mm] | per Reel | per Box | Hub Size<br>[mm] | Pockets | Length<br>[mm] | Pockets | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| STQFN<br>18L 0.4P<br>FC Green | 18           | 1.6 x 3 x 0.55       | 3,000    | 3,000   | 178 / 60         | 100     | 400            | 100     | 400            | 8             | 4             |

### **Carrier Tape Drawing and Dimensions**

| Package<br>Type               | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge | Index Hole<br>to Pocket<br>Center | Tape Width |

|-------------------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----------------------------------|------------|

|                               | Α0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F                                 | W          |

| STQFN 18L<br>0.4P FC<br>Green | 1.78                | 3.18               | 0.76            | 4                   | 4               | 1.5                    | 1.75                          | 3.5                               | 8          |

### **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 2.64 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

000-005NTH1011-100 Page 19 of 20

### **Revision History**

| Date     | Version | Change             |

|----------|---------|--------------------|

| 4/5/2017 | 1.00    | Production Release |

000-005NTH1011-100 Page 20 of 20