## ISSUE 1: Long RC OSC Settling Time Functional Block Affected: RC OSC, Counter, Delay

#### **Description:**

The RC OSC has a longer settling time when configured as 2 MHz with Auto Power On in the designs that have very short RC OSC disable time.

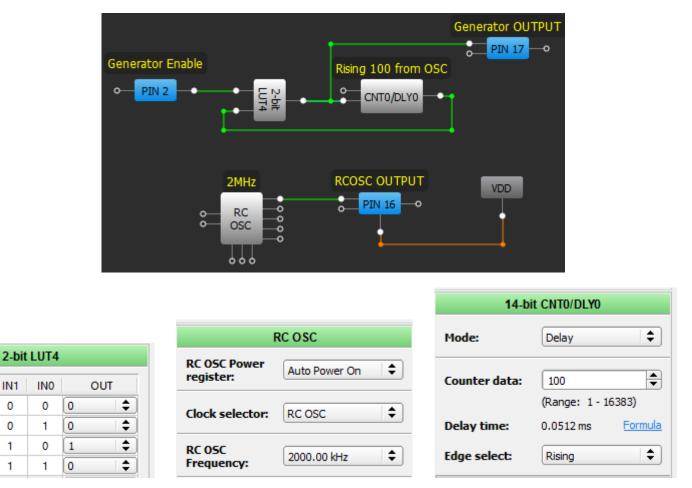

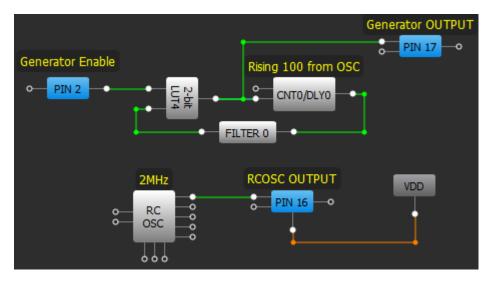

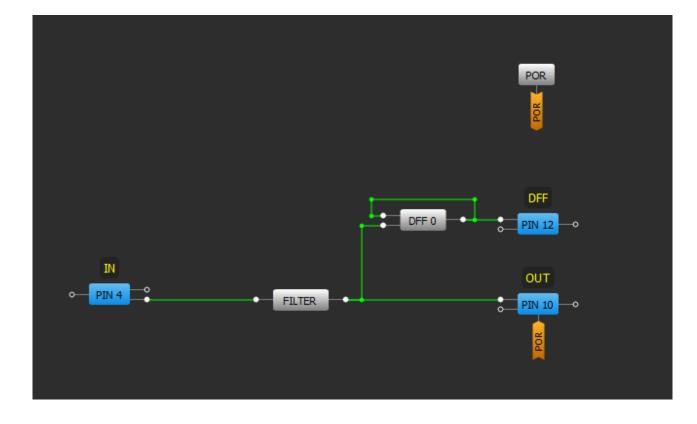

An example of such issue is in the following configuration:

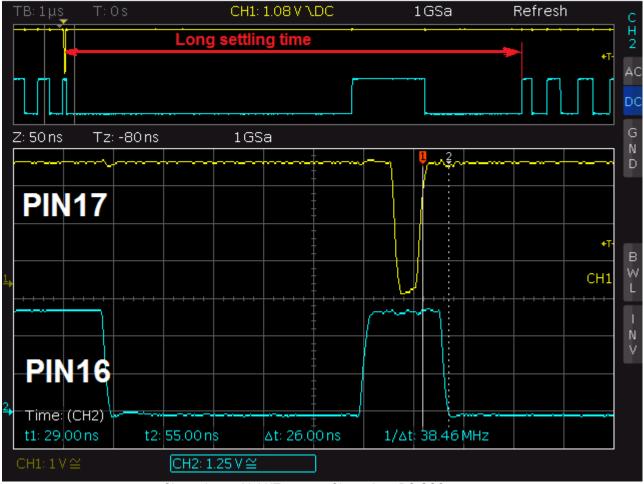

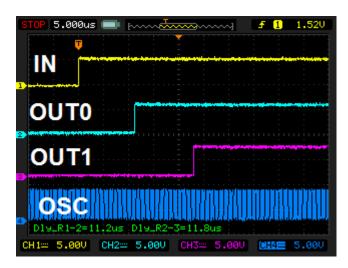

The configuration shown above generates a periodical signal with a frequency defined by the Delay cell and started by a high signal on PIN2. The issue becomes apparent in a longer settling time when the scheme generates short pulses (Delay is configured as a rising edge delay only). See waveform below.

## **SLG46722**

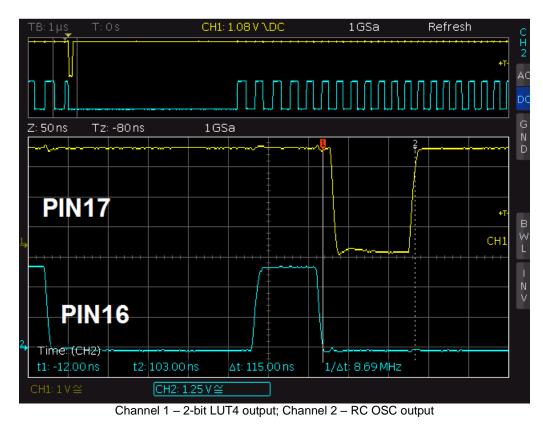

Channel 1 – 2-bit LUT4 output; Channel 2 – RC OSC output

Such behavior will lead to substantial error in period calculations if the delay time is relatively small.

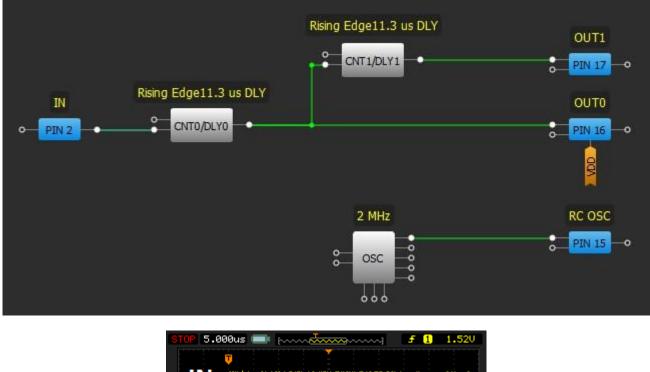

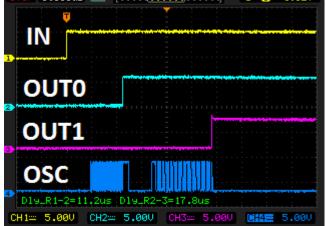

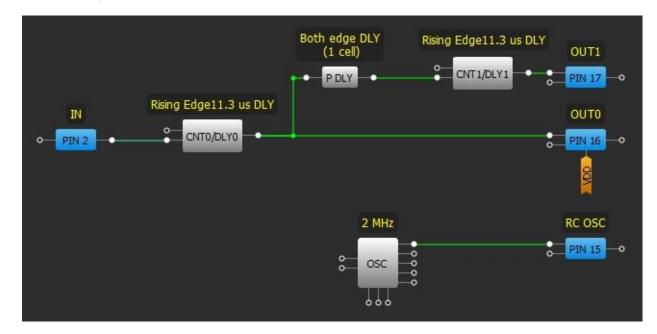

The same situation occurs while using two connected delays (all edge detect types except for a pair "Rising edge DLY – Falling edge DLY").

In the following example, Delay0 and Delay1 are configured in the same way. However, Delay1 time is 17.8us instead of expected 11.3us (Delay0 time).

If there are some inner blocks which use RC OSC at the moment or RC OSC is forced power on when such error appears, RC OSC will be operational and delay value will be proper.

#### Workaround:

In first case use block with longer propagation time. For example a Filter cell with an inverted output. Using two Filters in series or P DLY blocks in both edge delay mode (Delay time is 1 cell) for low power supply value (<3.3V) will result in a longer disable RC OSC time.

Using two delays in series (except for a pair "Rising edge DLY – Falling edge DLY") use one Filter cell or P DLY between delay blocks. Using LUTs won't help in this case.

Use the "Force power on" RC OSC power control option to make the RC OSC operate at all times.

### **ISSUE 2: LATCH Block nRESET Incorrect Operation** Functional Block Affected: LATCH

#### **Description:**

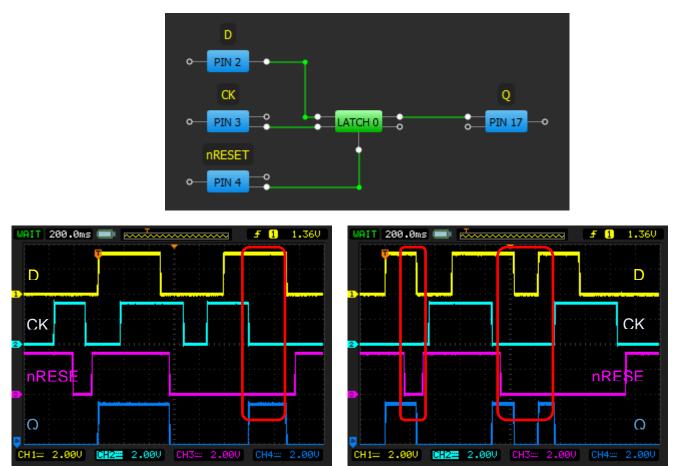

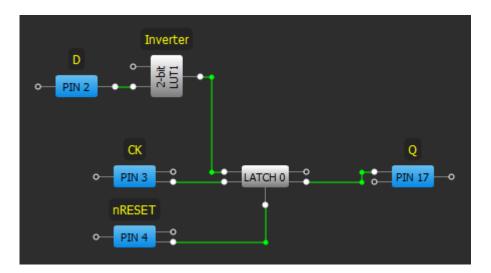

The reset function in LATCH blocks does not operate correctly. This can be described as function failure when nRESET input is set LOW.

The scope shots shown above show the incorrect nRESET function operation marked with red rectangles. From these waveforms can be seen that the reset function operates only when the CK signal is HIGH, in all other cases it is inoperational.

#### Workaround:

- Avoid using nRESET function in LATCH blocks in SLG46721/722 devices, if possible use SLG46110/120 devices, where this

function operates correctly.

- Use nSET configuration, initial state HIGH, add inverter on D input and use nQ (inverted) output of the LATCH block:

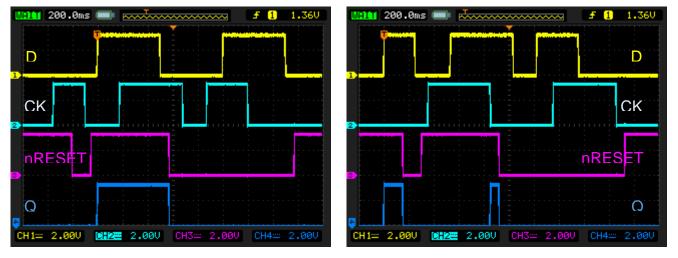

## ISSUE 3: Delay Lock-up by a Short Pulse Functional Block Affected: Delay

#### **Description:**

The delay output could be latched despite the input change when a short pulse is input. For example, if the delay cell is configured as a falling edge delay, the short pulse (see NOTE) appears on its input the delay cell output will switch from LOW to HIGH but may not switch from HIGH to LOW even after the delay time has passed.

NOTE: The pulse width varies from chip to chip and with different VDD voltage. It is in range of 5-15ns and in the window +/-0.2ns, so it should be very precise for issue happen.

**Revision 0.14**

7 of 13

Also, note that both edge delays do not have such issue.

#### Workaround:

- Use FILTER block on the Delay block input;

- Use P DLY block configured as a both edge delay.

### **ISSUE 4: FILTER cell does not filter out glitches** Functional Block Affected: FILTER

#### Description:

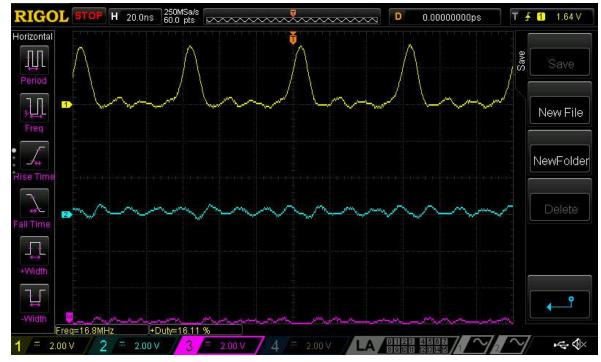

If clock type high frequency input comes in, the FILTER cell may not filter out it. There are several factors like input frequency, duty cycle and LOW duration in such signal that may lead to its passing through FILTER block.

## **SLG46722**

Channel 1 (yellow/top line) – PIN#4 (IN) Channel 2 (light blue/2nd line) – PIN#10 (OUT) Channel 3 (magenta /3rd line) – PIN#12 (DFF)

## **SLG46722**

1. Period is 60ns. Pulse width is 10ns DC=16.7% (Correct functionality)

2. Period is 60ns. Pulse width is 20ns DC = 33.3% (Incorrect functionality)

# **SLG46722**

3. Period is 60ns. Pulse width is 30ns DC=50% (Incorrect functionality)

4. Period is 60ns. Pulse width is 40ns DC=66.67% (Correct functionality)

<u>Workaround:</u> Currently there is no workaround for this issue. Filter block is good at filtering short spontaneous glitches. It is intended to be used in series connection before the delay cell to avoid its latching (see issue #4).

## SLG46722

#### Disclaimer

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semi-conductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2018 Dialog Semiconductor. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

## **Contacting Dialog Semiconductor**

#### United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

The Netherlands Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email: enquiry@diasemi.com North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japan Dialog Semiconductor K. K.

Phone: +81 3 5769 5100

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site: www.dialog-semiconductor.com Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

Korea Dialog Semiconductor Korea Phone: +82 2 3469 8200 China (Shenzhen) Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058

**Revision 0.14**

11-Apr-2019