**Company Confidential**

# Application Note PV88090 Voltage Rail Sequencing AN-PV-009

## **Abstract**

The application note describes control of the power rail sequencing of the PV88090 PMIC.

# **Company Confidential**

# **Contents**

| Contents                                                       | • |

|----------------------------------------------------------------|---|

| VOITOITO                                                       |   |

| Figures                                                        | 2 |

| 1 Introduction                                                 | 3 |

| 2 Sequencing                                                   | 3 |

| 2.1 General Power Sequencing Setting                           | 3 |

| 2.2 Specific Delay Time between Power Sequences                | 4 |

| 3 Conclusion                                                   | 6 |

| Revision History                                               | 7 |

|                                                                |   |

| Figures                                                        |   |

| Figure 1: Sequencing Slots Model                               | 3 |

| Figure 2: Sequencing Example and GUI Setting                   | 4 |

| Figure 3: Sequencing Waveform                                  |   |

| Figure 5: Example Sequencing with an Additional WAIT STEP Slot |   |

© 2018 Dialog Semiconductor

**Company Confidential**

#### 1 Introduction

PV88090 integrated three-channel PMIC incorporates advanced power sequencing that can be used to control the power up and power down sequence of its buck converters. It contains on-board OTP that is used to store the sequencing and this sequencing can also be controlled by an I<sup>2</sup>C command issued via the GUI or from the host processor. In applications requiring multiple PV88090s, GPIO and STBY pins can be used to control cascaded devices.

# 2 Sequencing

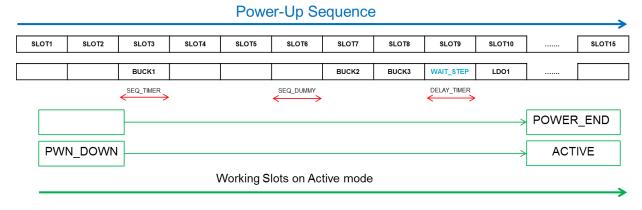

In the PV88090 digital system, there are 15 time slots used for sequencing. The system runs the time slots from 1 to 15 during the power on sequence, and runs back from 15 to 1 during the power down sequence. The available bucks should be assigned to slots between 1 and 15. The power on sequence, once arranged, can use the SYSTEM\_END parameter to separate the Standby mode and the Active mode operation. When STBY is pulled high, the system runs the sequence before the SYSTEM\_END slot. The system is now in the standby mode. When STBY is pulled low, all the slots run in sequence, the system is then in active mode, see Figure 1.

Note 1 If the standby pin is not used in your application, then SYSTEM\_END is not available.

A slot0 assignment means that function will not follow the power on or power off sequence. The buck assigned to slot0 will not be enabled in the power on sequence but can manually be turned on by I<sup>2</sup>C.

Figure 1: Sequencing Slots Model

There are two types of time slots, a normal slot which can be put in the sequence, like bucks or LDOs, and empty or "dummy slots". The time length can be set using SEQ\_DUMMY register bits. For example, slot1, slot2, slot4, and slot6 in Figure 1 are empty and are, therefore, dummy slots. The time length of both normal and dummy slots can be programed in register 0x17.

#### 2.1 General Power Sequencing Setting

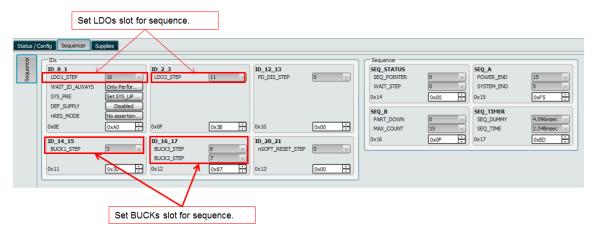

For general purpose sequencing, every buck converter should be assigned to a slot. Figure 2 shows an example of power sequencing. The power sequence follows the order assigned in the example, Buck1 [3], Buck2 [7], Buck3 [8], and LDO1 [10]. Every power rail can have its own slot number, two different power rails are allowed to be set to the same slot if they need to be turned on together. Set the SEQ\_TIME and SET\_DUMMY to adjust the slot time length, the delay time between the two different slots can be controlled.

**Company Confidential**

Figure 2: Sequencing Example and GUI Setting

By way of example, assume that a system requires Buck1 to turn on 14 ms earlier than Buck2 and Buck1  $\rightarrow$  <14 ms delay>  $\rightarrow$  Buck2  $\rightarrow$ <2 ms delay>  $\rightarrow$  Buck3.

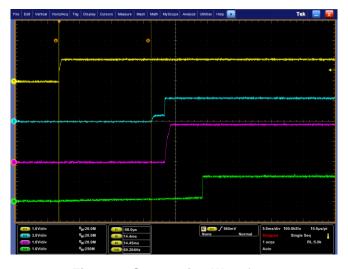

Set SEQ\_TIME = 2.048 ms, Buck1 set in slot3, Buck2 set in slot7, and Buck3 is in slot8, the delay time between Buck2 and Buck3 would be a normal sequence time so the result is 2 ms. Set the SET\_DUMMY = 4.096 ms, the delay time from Buck1 to Buck2 is a normal sequence time + 3 x dummy sequence time to gain the 14 ms delay time. The resulting sequence is shown in Figure 3.

The user can assign different combinations of slots and slot times to achieve the system requirement.

Figure 3: Sequencing Waveform

#### 2.2 Specific Delay Time between Power Sequences

In certain circumstances, a system may need a longer sequence than supported by the standard 15 slots + dummy slots.

For this situation, the PV88090 WAIT\_ID function can be used to insert a time slot to add a specific delay time.

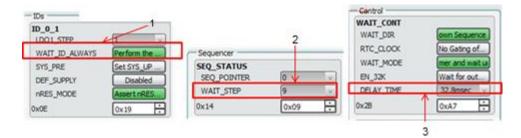

ID\_0 ((0x14[4:0]) is used to set the WAIT\_ID slot, it can be programmed to work for power up and power down sequences, or alternatively it can be programmed to operate on the first power on sequence.

**Company Confidential**

Figure 4: WAIT\_ID Behavior and Slot Setting

- **Note 1** Choose when the WAIT\_ID function is to be performed. This can be set to be only for the first power on or always.

- Note 2 Set which slot this WAIT\_STEP is to be performed, in this example slot9.

- Note 3 Set the period for DELAY\_TIME, which is 32.8 ms in this example.

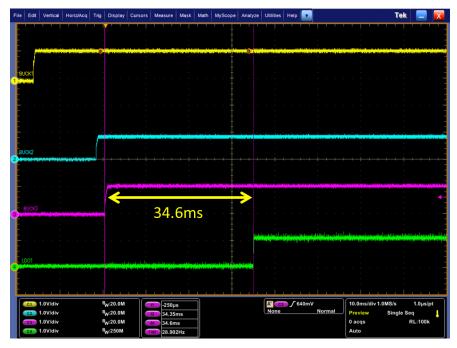

WAIT\_STEP can insert a specific delay time in the slot, the time length is set by DELAY\_TIME 0x39[0] with a range from 0 to 8.4 s. To illustrate the use of the WAIT\_ID function consider a system that needs a 34 ms delay between Buck3 and LDO1, keeping the original sequence time between Buck1, Buck2, and Buck3 as shown in Figure 3.

Set DELAY\_TIME = 32.8 ms and set WAIT\_ID in slot9. The delay time between Buck3 and LDO1 increases to 34.8 ms (typ). Figure 5 shows the result with an additional delay time in slot9 between Buck2 and Buck3.

Figure 5: Example Sequencing with an Additional WAIT\_STEP Slot

Depending on the system requirement, the WAIT\_ID slot can be set up to run during first time power up or every time the sequence is initiated:

- Turning off the WAIT\_ID \_ALWAYS, will set WAIT\_ID to First use, the WAIT\_ID delay time runs

once at power on reset. Afterwards it becomes a normal slot. When this field is off the

background color is gray.

- Turning on the WAIT\_ID \_ALWAYS, will set WAIT\_ID to Always, the WAIT\_ID performs a delay

every time the system runs the sequence (when coming out of standby). Afterwards it becomes a

normal slot. When this field is on the background color is green.

**Company Confidential**

# 3 Conclusion

PV88090 provides a flexible sequencing control via OTP and I<sup>2</sup>C setup and commands. This eases the burden on the BoM and PC space, provides a reduction in host GPIOs, and results in an improved reliability through the reduced component count.

**Company Confidential**

# **Revision History**

| Revision | Date        | Description                                              |

|----------|-------------|----------------------------------------------------------|

| 1.0      | 29-Dec-2017 | Updated Wait_ID_Always description                       |

| 0.3      | 20-Dec-2017 | Reviewed throughout and updated details on the last page |

| 0.2      | 12-Dec-2017 | Initial version                                          |

**Company Confidential**

#### **Status Definitions**

| Status               | Definition                                                                                                                   |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |  |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |  |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2018 Dialog Semiconductor. All rights reserved.

# **Contacting Dialog Semiconductor**

United Kingdom (Headquarters)

Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email:

enquiry@diasemi.com

North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222

Web site:

www.dialog-semiconductor.com

Hong Kong China

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200 China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai)

Dialog Semiconductor China Phone: +86 21 5424 9058

Application Note Revision 1.0 22-Jan-2017