# **DA9063L**

# System Power Management IC (PMIC) for Applications Providing up to 12 A Continuous Current

DA9063L is a powerful system PMIC for single-, dual-, and quad-core application processors such as those based on the ARM Cortex-A9TM and Cortex-A15TM architectures.

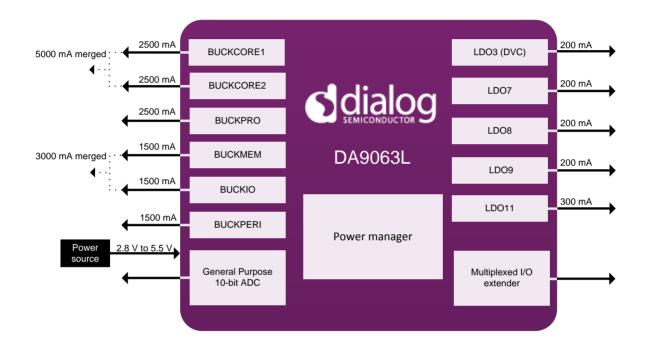

The DA9063L follows a scalable approach of output currents and rails to supply the entire system and is capable of delivering a total of up to 12 A from its six DC-DC buck converters. High efficiency is achieved over a wide load range by automatically selecting Pulse Frequency Modulation (PFM) or Pulse Width Modulation (PWM) modes. All bucks use integrated power switches, removing the need for external Schottky diodes. A high switching frequency allows low-profile inductors to be used. Two bucks can be combined in a 5 A dual- phase configuration, two offer a merged configuration for a combined 3 A, and one can be used as a DDR VTT supply. Five SmartMirror™ LDO regulators with programmable output voltage provide up to 300 mA.

All LDOs support remote capacitor placement and can operate from a low voltage supply. This allows the LDOs to be cascaded with a suitable buck to improve overall system efficiency. A number of LDOs can be configured as current-limited bypass-switches to support external peripherals.

Controlled by a programmable digital power manager, the 11 user-programmable switched/linear regulators may be configured to meet the start-up sequence, voltage, and timing requirements for most applications. The power manager includes supply-rail qualification and system reset management. Dynamic Voltage Scaling (DVS) is available to achieve optimal processor energy-per- task performance. Dialog's patented SmartMirror<sup>TM</sup> dynamic biasing is implemented on all linear regulators.

Power mode transitions can be triggered with software control, GPIOs, or with button control. Several types of button press can be used to trigger different power mode transitions. DVS can be realised via the I<sup>2</sup>C interface or GPIO control.

Available

Available in 100 VFBGA 8 mm x 8 mm x 1 mm, 0.8 mm pitch

16 GPIOs can be used to implement system functions such as: application wakeup; buffered 32kHz clock output; hardware regulator control; RGB-LED driver pins with PWM control; and sequencing control of external regulators, power switches, or other ICs such as the Dialog family of sub-PMICs.

An integrated 10-channel ADC includes advanced voltage monitoring, internal temperature supervision, three general-purpose channels with programmable high/low thresholds, an integrated current source for resistive measurements, and system voltage monitoring with a programmable low-voltage warning. The ADC has 8-bit resolution in AUTO mode and 10-bit resolution in manual conversion mode.

#### **Features**

- ▶ Input voltage 2.8 V to 5.5 V

- ► Six buck converters, 0.3 V to 3.34 V up to 2.5 A

- Dual-phase mode up to 5 A

- Merged mode up to 3 A

- DDR VTT supply mode

- DVS support

- ➤ 3 MHz switching frequency allows use of low-profile 1 µH inductors

- ► Integrated power switches

- ► 5 LDO regulators, 0.9 V to 3.6 V up to 300 mA

- 1 low-noise LDO

- 1 with DVS

- 4 with current-limited switch option

- ► I<sup>2</sup>C serial interface for system communication and control

- ► Programmable power manager

- System supply monitoring

- ▶ Junction temperature monitoring

- Watchdog timer

- ► 16 flexible GPIO pins for enhanced wakeup and peripheral control

- ► RGB-LED driver (PWM) with autonomous flashing

- PWM vibrator driver

- ► 10-bit ADC with nine channels and configurable alarm thresholds

- ► -40 °C to +125 °C junction temperature operation

- Automotive AEC-Q100 Grade 3 version

### **Applications**

- Portable industrial and medical devices

- ► TV donale

- ► Supply for single-, dual- and quad-core application processors, for example the i.MX<sup>TM</sup> families

- eReaders

- Power supply for FPGAs

- ► Automotive infotainment/dashboard

- ▶ IoT devices

## **Block Diagram**

## **Generated Supply Domains**

| Block     | Supplied<br>Voltage (V) | Supplied<br>Max.<br>Current (A) | External<br>Components | Notes                                                                                                          |

|-----------|-------------------------|---------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------|

| BUCKCORE1 | 0.3 to 1.57             | 2.5                             | 1.0 μΗ / 2 x 47 μF     | 3 MHz, DVS with variable slew rate,<br>10 mV steps                                                             |

| BUCKCORE2 | 0.3 to 1.57             | 2.5                             | 1.0 μH / 2 x 47 μF     | 3 MHz, DVS with variable slew rate,<br>10 mV steps, can be combined with<br>BUCKCORE1 as a 5 A dual-phase buck |

| BUCKPRO   | 0.53 to 1.80            | 2.5                             | 1.0 μH / 2 x 47 μF     | 3 MHz, DVS with variable slew rate,<br>10 mV steps, can be used as a DDR<br>VTT supply                         |

| BUCKMEM   | 0.8 to 3.34             | 1.5                             | 1.0 μH / 2 x 22 μF     | 3 MHz, DVS with variable slew rate,<br>20 mV steps, 3 A merged mode with<br>BUCKIO                             |

| BUCKIO    | 0.8 to 3.34             | 1.5                             | 1.0 μH / 2 x 22 μF     | 3 MHz, DVS with variable slew rate,<br>20 mV steps                                                             |

| BUCKPERI  | 0.8 to 3.34             | 1.5                             | 1.0 μH / 2 x 22 μF     | 3 MHz, DVS with variable slew rate,<br>20 mV steps                                                             |

| LDO3      | 0.9 to 3.44             | 0.2                             | 2.2 µF                 | Bypass mode, 20 mV steps, DVS with variable slew rate                                                          |

| LDO7      | 0.9 to 3.6              | 0.2                             | 2.2 μF                 | Bypass mode, 50 mV steps                                                                                       |

| LDO8      | 0.9 to 3.6              | 0.2                             | 2.2 µF                 | Bypass mode, switching vibration motor driver mode, 50 mV steps                                                |

| LDO9      | 0.95 to 3.6             | 0.2                             | 2.2 μF                 | Low noise, 50 mV steps                                                                                         |

| LDO11     | 0.9 to 3.6              | 0.3                             | 2.2 µF                 | Bypass mode, 50 mV steps                                                                                       |

#### Dialog Semiconductor Worldwide Sales Offices - www.dialog-semiconductor.com email: info@diasemi.com

United Kingdom Phone: +44 1793 757700

The Netherlands Phone: +31 73 640 88 22 Japan Phone: +81 3 5425 4567

Singapore Phone: +65 648 499 29 Korea

Phone: +82 2 3469 8200

Phone: +49 7021 805-0

North America Phone: +1 408 845 8500 Phone: +886 281 786 222

Hong Kong Phone: +852 3769 5200

China (Shenzhen) Phone: +86 755 2981 3669

China (Shanghai) Phone: +86 21 5424 9058

This publication is issued to provide outline information only, which unless agreed by Dialog Semiconductor may not be used, applied, or reproduced for any purpose or be regarded as a representation relating to products. All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's <a href="Standard Terms and Conditions of Sale">Standard Terms and Conditions of Sale</a>, available on the company website (<a href="www.dialog-semiconductor.com">www.dialog-semiconductor.com</a>) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.