# Application Note DA9061 / AtlasVI Power Connections

# **AN-PM-082**

## Abstract

This document describes the connectivity between the Dialog DA9061 Power Management Integrated Circuit (PMIC) and Qualcomm AtlasVI™ system processor.

## **AN-PM-082**

## DA9061 / AtlasVI Power Connections

## Contents

| Ab  | stract | t                                                   | 1 |

|-----|--------|-----------------------------------------------------|---|

| Co  | ntent  | S                                                   | 2 |

| Fig | jures. |                                                     | 2 |

| Та  | bles   |                                                     | 2 |

| 1   | Term   | ns and Definitions                                  |   |

| 2   | Refe   | rences                                              |   |

| 3   | Intro  | oduction                                            | 4 |

| 4   | Syst   | em Block Diagram                                    | 4 |

| 5   |        | ng Diagrams                                         |   |

|     | 5.1    | Cold Boot                                           |   |

|     | 5.2    | Power-Down                                          | 7 |

|     | 5.3    | Power-Up                                            |   |

|     | 5.4    | Software Initiated Power-Down                       | 9 |

|     | 5.5    | Watchdog Reset (No Freeze)                          |   |

|     | 5.6    | Watchdog Reset (With Freeze)                        |   |

|     | 5.7    | Temperature Warning and Temperature Error           |   |

|     | 5.8    | Temperature Power-On Reset                          |   |

|     | 5.9    | System Supply Under-Voltage                         |   |

| 6   | Soft   | ware Driver                                         |   |

| 7   | Deve   | elopment Support Tools and PMIC Configuration Files |   |

| 8   | Devi   | ce Identification and Ordering                      |   |

| Re  | visior | n History                                           |   |

# **Figures**

| Figure 1: DA9061 to AtlasVI Mapping                                    | 4    |

|------------------------------------------------------------------------|------|

| Figure 2: Timing Diagram for Cold Boot                                 |      |

| Figure 3: Timing Diagram for Power-Down                                |      |

| Figure 4: Timing Diagram for Power-Up                                  |      |

| Figure 5: Timing Diagram for a Software Initiated Power-Down           |      |

| Figure 6: Timing Diagram for Watchdog Reset                            |      |

| Figure 7: Timing Diagram for Watchdog Reset Causing a Freeze           | . 11 |

| Figure 8: Timing Diagram for Temperature Warning and Temperature Error |      |

| Figure 9: Timing Diagram for Temperature Power-On Reset                |      |

| Figure 10: Timing Diagram for System Supply Under-Voltage              |      |

|                                                                        |      |

## **Tables**

| Table 1: GPIO Mapping for AtlasVI | 5  |

|-----------------------------------|----|

| Table 2: Product Part Numbers     | 15 |

## **AN-PM-082**

#### **DA9061 / AtlasVI Power Connections**

## **1** Terms and Definitions

| GUI     | Graphical User Interface                         |

|---------|--------------------------------------------------|

| AtlasVI | Qualcomm SoC, formally known as CSR SiRFatlasVI™ |

| SoC     | System on a Chip                                 |

| PMIC    | Power Management Integrated Circuit              |

## 2 References

- [1] DA9061, Datasheet, Dialog Semiconductor

- [2] SiRFatlasVI, http://www.csr.com/products/148/sirfatlasvi [Accessed 14-Jul-2016]

- [3] DA9062, Datasheet, Dialog Semiconductor

- [4] The Linux Kernel Archives, https://kernel.org/ [Accessed 13-Sep-2016]

## 3 Introduction

This document provides details of integrating the DA9061 with the AtlasVI SoC [2], suitable for lowend and mid-range infotainment applications. For high-end applications, integration of Dialog DA9062 [3] and Atlas7<sup>™</sup> is recommended.

## 4 System Block Diagram

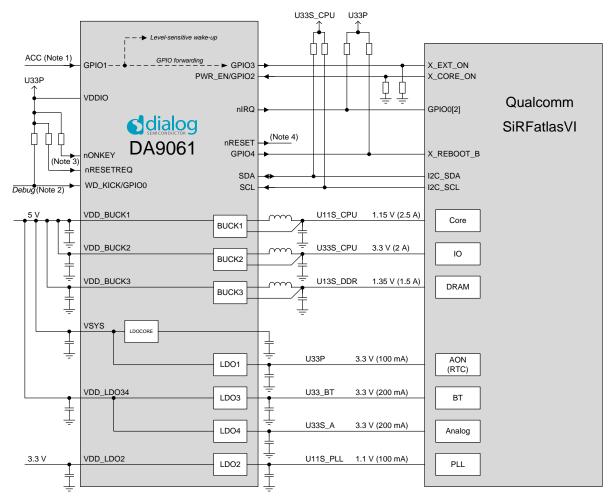

#### Figure 1: DA9061 to AtlasVI Mapping

- Note 1 The ACC GPIO1 signal is to be derived from the 12 V ACC (automotive) accessory line.

- **Note 2** The WD\_KICK/GPIO0 input requires a pulse every 2 s (as set by register control TWDSCALE). Alternatively, the input can be permanently asserted using the pull-up shown. This may be useful during application debugging.

- **Note 3** nONKEY is not used. System start-up is initiated by ACC / GPIO1.

- **Note 4** nRESET is not used.

# AN-PM-082

#### **DA9061 / AtlasVI Power Connections**

#### Table 1: GPIO Mapping for AtlasVI

| GPIO  | Function                                | Description                                         |

|-------|-----------------------------------------|-----------------------------------------------------|

| GPIO0 | WD_KICK                                 | Watchdog kick/disable                               |

| GPIO1 | GPI                                     | ACC in (derived from the 12 V ACC accessory line)   |

| GPIO2 | PWR_EN                                  | Power enable                                        |

| GPIO3 | GPO push-pull<br>(forwarded from GPIO1) | ACC out                                             |

| GPIO4 | GPO push-pull                           | Core reset for AtlasVI, controlled by the sequencer |

**Application Note**

## 5 Timing Diagrams

The numbered notes below each figure correspond to the numbered events within the figure.

## 5.1 Cold Boot

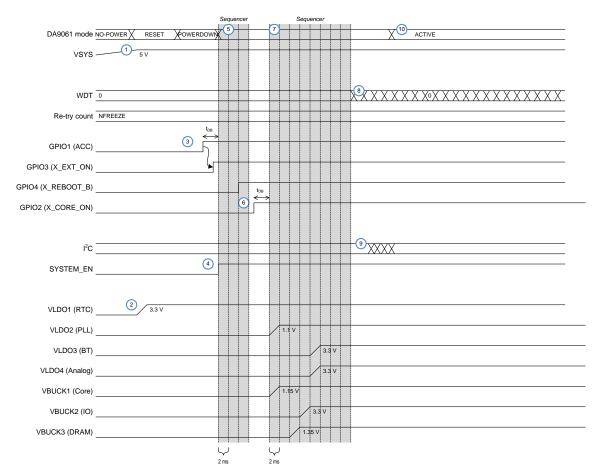

#### Figure 2: Timing Diagram for Cold Boot

- 1. The system supply rises above a threshold value after which the internal supplies of DA9061 are enabled and the device enters the RESET mode and then automatically proceeds to the POWERDOWN mode.

- 2. The always-on supply LDO1 is enabled in the RESET mode.

- GPIO1 (ACC) is asserted (level-sensitive signal) which triggers a power-up sequence, and the signal is also forwarded to GPIO3 (X\_EXT\_ON). The delay between the rising edge of the GPIO1 (ACC) and the sequence starting is defined by the debouncing time t<sub>DB</sub>.

- 4. A partial OTP read is executed at the beginning of the power-up sequence which asserts control SYSTEM\_EN.

- DA9061 executes the first part of the power-up sequence during which GPIO4 (X\_REBOOT\_B) is de-asserted.

- AtlasVI asserts the X\_CORE\_ON signal which triggers the second part of the power-up sequence. The delay between the rising edge of the GPIO2/PWR\_EN (X\_CORE\_ON) and the sequence starting is defined by the de-bouncing time t<sub>DB</sub>.

- 7. DA9061 executes the second part of the power-up sequence during which the supplies are enabled in the programmed order. The time between the sequencer steps is 2 ms.

- 8. The watchdog starts running when the power-up sequence completes.

- 9. AtlasVI software performs the first watchdog kick through  $I^2C$ .

- 10. DA9061 enters the ACTIVE mode.

| Арр | lication | Note |

|-----|----------|------|

|-----|----------|------|

#### Revision 1.0

15-Sep-2016

## 5.2 Power-Down

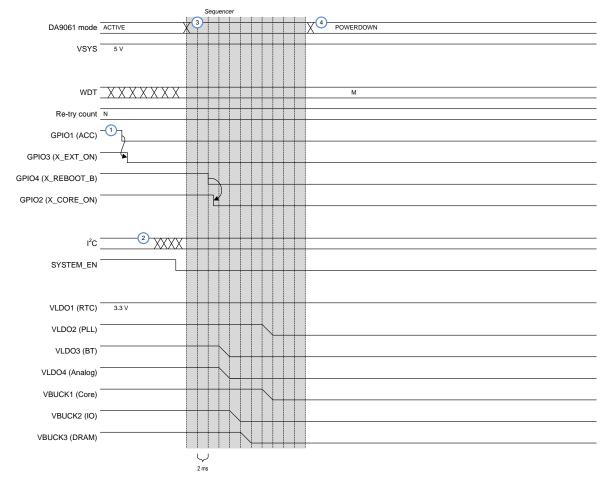

#### Figure 3: Timing Diagram for Power-Down

- 1. GPIO1 (ACC) is de-asserted and the signal is forwarded to GPIO3 (X\_EXT\_ON).

- 2. AtlasVI software sees the de-asserted X\_EXT\_ON and performs necessary preparations for power-down and then de-asserts control SYSTEM\_EN through I<sup>2</sup>C.

- 3. DA9061 executes the power-down sequence during which GPIO4 (X\_REBOOT\_B) is asserted and supplies are disabled in the reverse order. X\_CORE\_ON is de-asserted asynchronously when GPIO4 (X\_REBOOT\_B) is asserted. The time between the sequencer steps is 2 ms, because the power-down was triggered by de-asserting control SYSTEM\_EN, the sequencer proceeds directly to the POWERDOWN mode.

- 4. DA9061 completes the power-down sequence and enters the POWERDOWN mode. The watchdog is not counting in POWERDOWN mode.

| -  |      |      |     |     |

|----|------|------|-----|-----|

| Δn | nlic | atic | n N | ote |

| ΠP | piic | anc  |     | Ole |

## 5.3 Power-Up

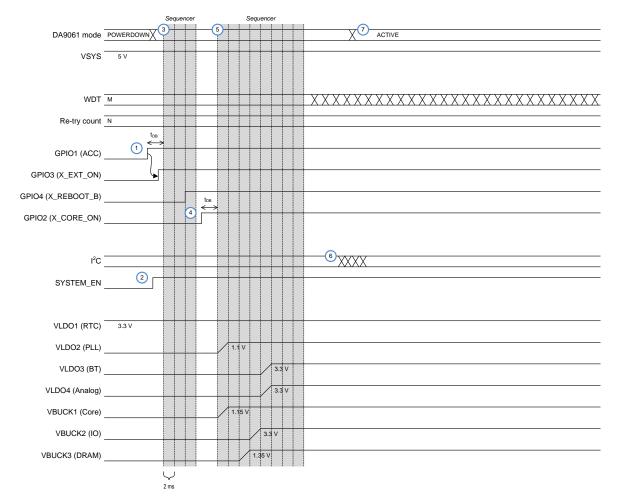

#### Figure 4: Timing Diagram for Power-Up

- GPIO1 (ACC) is asserted (level-sensitive signal) which triggers a power-up sequence, and the signal is also forwarded to GPIO3 (X\_EXT\_ON). The delay between the rising edge of the GPIO1 (ACC) and the sequence starting is defined by the de-bouncing time t<sub>DB</sub>.

- 2. A partial OTP read is executed at the beginning of the power-up sequence which asserts control SYSTEM\_EN.

- 3. DA9061 executes the first part of the power-up sequence during which GPIO4 (X\_REBOOT\_B) is de-asserted.

- AtlasVI asserts the X\_CORE\_ON signal which triggers the second part of the power-up sequence. The delay between the rising edge of the PWR\_EN (X\_CORE\_ON) and the sequence starting is defined by the de-bouncing time t<sub>DB</sub>.

- 5. DA9061 executes the second part of the power-up sequence during which the supplies are enabled in the programmed order. The timing between the sequencer steps is 2 ms.

- 6. AtlasVI software performs the first watchdog kick through  $I^2C$ .

- 7. DA9061 enters the ACTIVE mode.

## 5.4 Software Initiated Power-Down

#### Figure 5: Timing Diagram for a Software Initiated Power-Down

- 1. AtlasVI software re-configures GPIO1 from level sensitive to edge sensitive.

- 2. AtlasVI software performs necessary preparations for a power-down and then de-asserts control SYSTEM\_EN through I<sup>2</sup>C.

- 3. DA9061 executes the power-down sequence as described in Section 5.2.

- 4. DA9061 completes the power-down sequence and enters the POWERDOWN mode. The watchdog is not counting in POWERDOWN mode. Because GPIO1 (ACC) was re-configured as edge sensitive a power-up sequence is not triggered by the GPIO1 (ACC) level.

- 5. GPIO1 (ACC) is de-asserted.

- 6. GPIO1 (ACC) is asserted and the detected rising edge triggers a power-up sequence. The signal is also forwarded to GPIO3 (X\_EXT\_ON).

- 7. DA9061 executes the power-up sequence as described in Section 5.3. During the power-up sequence, an OTP read is executed that restores the GPIO1 (ACC) setting as level sensitive.

- 8. DA9061 completes the power-up sequence and the watchdog continues running.

- 9. AtlasVI software performs a watchdog kick through I<sup>2</sup>C.

- 10. DA9061 enters the ACTIVE mode.

#### **Application Note**

## 5.5 Watchdog Reset (No Freeze)

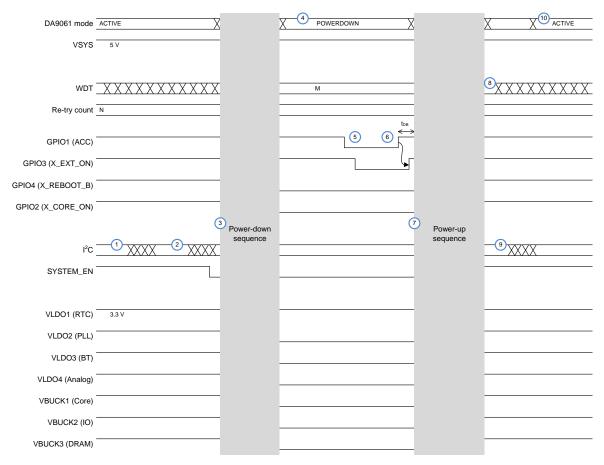

#### Figure 6: Timing Diagram for Watchdog Reset

- 1. The watchdog timer reaches its maximum value causing a watchdog error. This de-asserts control SYSTEM\_EN which triggers a power-down sequence.

- 2. The re-try counter is decremented as a result of the watchdog error.

- 3. The sequencer executes the power-down sequence as described in Section 5.2

- 4. The power-down sequence is completed and DA9061 enters the POWERDOWN mode but because GPIO1 (ACC) remains asserted a new power-up sequence is immediately triggered.

- 5. DA9061 executes the power-up sequence as described in Section 5.3.

- 6. DA9061 completes the power-up sequence and the watchdog continues running.

- 7. AtlasVI software performs a watchdog kick through I<sup>2</sup>C.

- 8. DA9061 enters the ACTIVE mode.

| App | lication | Note |

|-----|----------|------|

|     | noution  | HOLE |

## 5.6 Watchdog Reset (With Freeze)

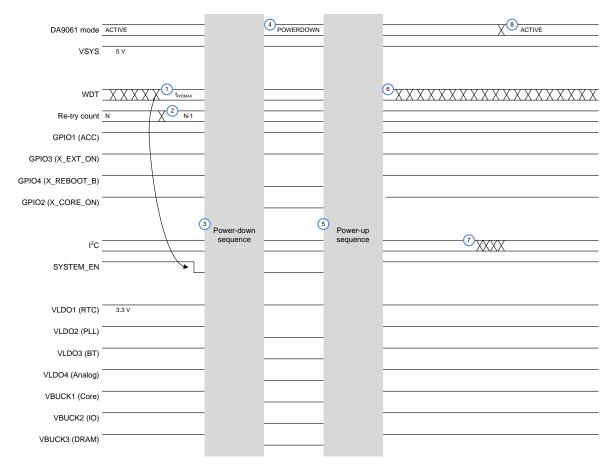

#### Figure 7: Timing Diagram for Watchdog Reset Causing a Freeze

- 1. The watchdog timer reaches its maximum value causing a watchdog error. This de-asserts control SYSTEM\_EN which triggers a power-down sequence.

- 2. The re-try counter is decremented as a result of the watchdog error. This time, the re-try count reaches zero which causes the freeze function to be activated.

- 3. The sequencer executes the power-down sequence as described in Section 5.2.

- 4. The power-down sequence is completed and DA9061 enters the POWERDOWN mode. Because the freeze function is active, a power-up sequence is not triggered even though ACC remains asserted.

- 5. GPIO1 (ACC) is de-asserted.

- 6. As a result of the de-asserted level sensitive wakeup, the re-try counter is reset and the freeze function is de-activated.

- GPIO1 (ACC) is re-asserted which triggers a power-up sequence, and the signal is also forwarded to GPIO3 (X\_EXT\_ON). The delay between the rising edge of the GPIO1 (ACC) and the sequence starting is defined by the de-bouncing time t<sub>DB</sub>.

- 8. DA9061 executes the power-up sequence as described in Section 5.3.

- 9. DA9061 completes the power-up sequence and the watchdog continues running.

- 10. AtlasVI software performs a watchdog kick through I<sup>2</sup>C.

- 11. DA9061 enters the ACTIVE mode.

#### **Application Note**

## 5.7 Temperature Warning and Temperature Error

| 150 °C<br>T」 140 °C<br>125 °C |           | -         | 8        |

|-------------------------------|-----------|-----------|----------|

| E_TEMP                        |           |           | 1        |

| nIRQ                          |           |           |          |

| TEMP_CRIT                     |           |           |          |

|                               |           |           |          |

| DA9061 mode                   | ACTIVE    |           | -7-RESET |

| VSYS                          | 5 V       |           |          |

|                               |           |           |          |

| WDT                           | ****      |           | 0        |

| Re-try count                  | N         |           | NFREEZE  |

| GPIO1 (ACC)                   |           |           |          |

| GPIO3 (X_EXT_ON)              |           |           |          |

| GPIO4 (X_REBOOT_B)            |           |           |          |

| GPIO2 (X_CORE_ON)             |           |           |          |

|                               | (0        | Shut-down |          |

| l <sup>2</sup> C              | 3<br>XXXX | sequence  |          |

| SYSTEM_EN                     |           |           |          |

|                               |           |           |          |

| VLDO1 (RTC)                   | 3.3 V     |           |          |

| VLDO2 (PLL)                   |           |           |          |

| VLDO3 (BT)                    |           |           |          |

| VLDO4 (Analog)                |           |           |          |

| VBUCK1 (Core)                 |           |           |          |

| VBUCK2 (IO)                   |           |           |          |

| VBUCK3 (DRAM)                 |           |           |          |

#### Figure 8: Timing Diagram for Temperature Warning and Temperature Error

- 1. The die temperature exceeds  $T_{WARN}$  which causes the event E\_TEMP to be asserted. The event, if not masked, asserts nIRQ.

- 2. AtlasVI software sees the temperature warning and reduces the activity of the platform.

- 3. AtlasVI software clears the event E\_TEMP. If no other events are active, this de-asserts nIRQ.

- The die temperature exceeds T<sub>WARN</sub> again which causes the event E\_TEMP to be asserted. The event, if not masked, asserts nIRQ.

- 5. The die temperature exceeds T<sub>CRIT</sub> which causes the temperature error flag TEMP\_CRIT to be asserted, and a shut-down sequence is triggered.

- 6. DA9061 executes the shut-down sequence which is the same as the power-down sequence described in Section 5.2, but a shut-down sequence triggered by a temperature error proceeds straight to the RESET mode.

- 7. DA9061 completes the shut-down sequence and enters the RESET mode. The re-try count is reset, but the temperature error flag is not reset.

- DA9061 stays in RESET mode as long as the die temperature stays above T<sub>CRIT</sub>. After this, the power-up sequence is executed in the same way as in the cold boot use case described in Section 5.1.

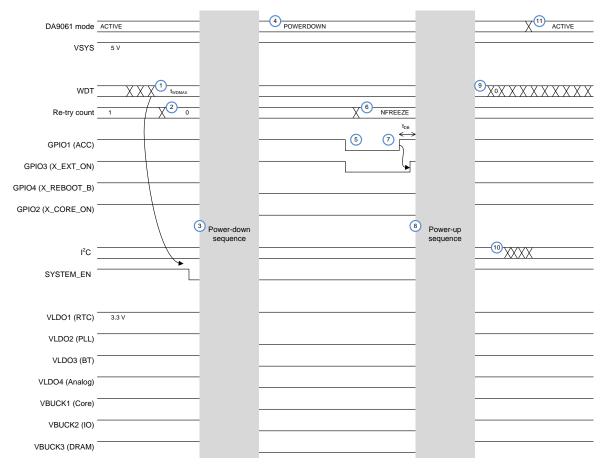

## 5.8 Temperature Power-On Reset

| 150 °C                | •      |           | 5        |

|-----------------------|--------|-----------|----------|

| T <sub>J</sub> 140 °C | 2      |           | T        |

| 125 °C                | 0      |           |          |

| 125 6                 |        |           |          |

|                       | /      |           |          |

|                       |        |           |          |

| E_TEMP                |        |           |          |

|                       |        | ,         |          |

| nIRQ                  |        |           |          |

|                       |        |           |          |

| TEMP_CRIT             |        |           | 7        |

| +                     |        |           |          |

|                       |        |           |          |

|                       |        |           |          |

| DA9061 mode           | ACTIVE |           | RESET    |

|                       |        |           | <u>\</u> |

| VSYS                  | 5 V    |           |          |

|                       |        |           |          |

|                       |        |           |          |

|                       |        |           |          |

| WDT                   |        |           | 0        |

|                       |        |           |          |

| Re-try count          | Ν      |           | NFREEZE  |

|                       |        |           |          |

| GPIO1 (ACC)           |        |           |          |

|                       |        |           |          |

| GPIO3 (X_EXT_ON)      |        |           |          |

|                       |        |           |          |

| GPIO4 (X_REBOOT_B)    |        |           |          |

|                       |        |           |          |

| GPIO2 (X_CORE_ON)     |        |           |          |

|                       | 3      |           |          |

|                       |        | Shut-down |          |

| I <sup>2</sup> C      |        | sequence  |          |

| 10                    |        |           |          |

| SYSTEM_EN             |        |           |          |

| OTOTEM_EN             |        |           |          |

|                       |        |           |          |

|                       |        |           |          |

| VLDO1 (RTC)           | 3.3 V  |           |          |

|                       |        |           |          |

| VLDO2 (PLL)           |        |           |          |

|                       |        |           |          |

| VLDO3 (BT)            |        |           |          |

|                       |        |           |          |

| VLDO4 (Analog)        |        |           |          |

|                       |        |           |          |

| VBUCK1 (Core)         |        |           |          |

|                       |        |           |          |

| VBUCK2 (IO)           |        |           |          |

|                       |        |           |          |

| VBUCK3 (DRAM)         |        |           |          |

#### Figure 9: Timing Diagram for Temperature Power-On Reset

- 1. The die temperature exceeds T<sub>WARN</sub> which causes the event E\_TEMP (in register EVENT\_B) to be asserted. The event, if not masked, asserts nIRQ.

- The die temperature exceeds T<sub>CRIT</sub> which causes the temperature error flag TEMP\_CRIT (in register FAULT\_LOG) to be set, and a shut-down sequence is triggered.

- 3. DA9061 executes the shut-down sequence which is the same as the power-down sequence described in Section 5.2 but a shut-down sequence triggered by over-temperature proceeds straight to the RESET mode.

- 4. The die temperature exceeds  $T_{POR}$  which causes DA9061 to enter the RESET mode without any sequencing. Also the always-on LDO1 is disabled.

- DA9061 stays in the RESET mode as long as the temperature stays above T<sub>CRIT</sub>. After this a cold boot is executed as described in Section 5.1.

## 5.9 System Supply Under-Voltage

| V <sub>SYS</sub>                |          |                       |                      |

|---------------------------------|----------|-----------------------|----------------------|

| V <sub>DD_FAULT_UPPER</sub>     |          |                       |                      |

| VDD_FAULT_LOWER                 |          |                       | 9                    |

| E_VDD_WARN<br>nIRQ<br>VDD_FAULT |          |                       |                      |

| DA9061 mode                     | ACTIVE X |                       | X <sup>®</sup> RESET |

| WDT                             |          |                       | 0                    |

| Re-try count                    | N        |                       | NFREEZE              |

| GPIO1 (ACC)                     |          |                       |                      |

| GPIO3 (X_EXT_ON)                |          |                       |                      |

| GPIO4 (X_REBOOT_B)              |          |                       |                      |

| GPIO2 (X_CORE_ON)               |          |                       |                      |

| l²c<br>system_en                |          | Shut-down<br>sequence |                      |

| VLDO1 (RTC)                     | 3.3 V    |                       |                      |

| VLDO2 (PLL)                     | v c.c    |                       |                      |

|                                 |          |                       |                      |

| VLDO3 (BT)                      |          |                       |                      |

| VLDO4 (Analog)                  |          |                       |                      |

| VBUCK1 (Core)                   |          |                       |                      |

| VBUCK2 (IO)                     |          |                       |                      |

| VBUCK3 (DRAM)                   |          |                       |                      |

#### Figure 10: Timing Diagram for System Supply Under-Voltage

- The system supply (V<sub>SYS</sub>) drops below V<sub>DD\_FAULT\_UPPER</sub> which causes the event E\_VDD\_WARN (in register EVENT\_B) to be asserted. The event, if not masked, asserts nIRQ.

- 2. AtlasVI software sees the system supply warning and reduces the activity of the platform. This should reduce the current draw of the platform and stabilize the system supply.

- AtlasVI software clears the event E\_VDD\_WARN. If no other events are active, this de-asserts nIRQ.

- The system supply recovers above the V<sub>DD\_FAULT\_UPPER</sub> threshold. After this, there is a 1 s

debounce period for V<sub>SYS</sub>. During this period the system supply comparators are not enabled and

if V<sub>SYS</sub> drops below V<sub>DD\_FAULT\_UPPER</sub> no event is generated.

- 5.  $V_{SYS}$  drops below  $V_{DD_{FAULT_{UPPER}}}$  again which causes the event E\_VDD\_WARN to be asserted. The event, if not masked, asserts nIRQ.

- V<sub>SYS</sub> drops below V<sub>DD\_FAULT\_LOWER</sub> which causes the system supply error flag VDD\_FAULT (in register FAULT\_LOG) to be set, and a shut-down sequence is triggered.

- DA9061 executes a shut-down sequence which the same as the power-down sequence described in Section 5.2 but a shut-down sequence triggered by a voltage error proceeds directly to the RESET mode.

|    | 1.00  |       |    |    |

|----|-------|-------|----|----|

| AD | olica | ation | NO | te |

- 8. DA9061 completes the shut-down sequence and enters the RESET mode. The re-try count is reset but the system supply error flag is not.

- 9. DA9061 stays in RESET mode as long as the system supply stays below VDD\_FAULT\_LOWER. After this, the power-up sequence is executed in the same way as in the cold boot use case described in Section 5.1.

## 6 Software Driver

After the DA9061 has started the AtlasVI system, software can read and write to the PMIC via the I<sup>2</sup>C bus. This can be used for further PMIC configuration, such as the GPIOs, interrupt servicing, watchdog 'keep-alive' writes, and so on. Dialog drivers for Linux<sup>™</sup> are available in the Linux kernel from https://kernel.org/ [4] or, if interim assistance is required, from your Dialog Sales representative.

## 7 Development Support Tools and PMIC Configuration Files

To assist with hardware and software development, Dialog provides the following:

• DA9061 Evaluation Kit

This contains motherboard and daughterboard for hardware evaluation and software development. It also includes the SmartCanvas™ GUI software.

SmartCanvas GUI

This is PC-driven software to provide easy access to a device under test (DUT). The GUI is used to exercise the DUT using the I<sup>2</sup>C interface. Control or measurement of analog and digital pins is supported. SmartCanvas supports the Dialog PMIC OTP configuration file (.ini file) format.

• OTP configuration .ini file DA9061-03\_Atlas6\_0v1\_547A.ini

This file defines the configuration of the DA9061 at boot. The file is available from the Dialog Support website. The .ini file is opened using the SmartCanvas GUI.

• Linux software driver. See Section 6.

## 8 Device Identification and Ordering

Available parts are shown in Table 2. If the DA9061-03 proves unsuitable for your target AtlasVI design, please contact your Dialog sales representative to discuss custom variants. (Minimum order quantities apply for custom variants.)

Table 2: Product Part Numbers

| Part Number    | Description (Note 1)        |  |

|----------------|-----------------------------|--|

| DA9061-03AMx   | Industrial grade            |  |

| DA9061-03AMx-A | Automotive AEC-Q100 Grade 3 |  |

Note 1 See the DA9061 datasheet [1] for further information regarding part ordering. All parts are available in Tray (x = 1) or Tape & Reel (x = 2).

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 15-Sep-2016 | Initial version |

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2016 Dialog Semiconductor. All rights reserved.

## **Contacting Dialog Semiconductor**

United Kingdom (Headquarters) Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

#### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822 Email:

enquiry@diasemi.com

# Application Note

#### North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japan

Dialog Semiconductor K. K. Phone: +81 3 5425 4567

#### Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222 Web site:

www.dialog-semiconductor.com

#### Singapore

Dialog Semiconductor Singapore Phone: +65 64 8499 29

#### Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 3769 5200

#### Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200

#### China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai) Dialog Semiconductor China Phone: +86 21 5424 9058

CFR0014

15-Sep-2016