# Application Note DA9063 Voltage Monitoring AN-PM-024

# Abstract

This application note supplements the DA9063 datasheet with further detail of the monitoring feature for the input voltage (VSYS) and output voltages (LDOs, bucks), and also describes manual monitoring of rails

# **AN-PM-024**

# DA9063 Voltage Monitoring

# Contents

| Ab  | stract                         |                   |                                               | 1 |  |  |  |  |

|-----|--------------------------------|-------------------|-----------------------------------------------|---|--|--|--|--|

| Co  | Contents 2                     |                   |                                               |   |  |  |  |  |

| Fig | Figures                        |                   |                                               |   |  |  |  |  |

| Ta  | bles                           |                   |                                               | 3 |  |  |  |  |

| 1   | Term                           | s and De          | finitions                                     | 4 |  |  |  |  |

| 2   | Refer                          | ences             |                                               | 4 |  |  |  |  |

| 3   | Introd                         | duction           |                                               | 5 |  |  |  |  |

| 4   | Signa                          | als and R         | egisters Overview                             | 5 |  |  |  |  |

| 5   | VSYS                           | 6 Monitor         | ing                                           | 6 |  |  |  |  |

|     | 5.1                            | VSYS U            | nder-Voltage, E_VDD_WARN, nIRQ and nVDD_FAULT | 6 |  |  |  |  |

|     | 5.2                            | VDD_M             | ON, nIRQ                                      | 6 |  |  |  |  |

|     |                                | 5.2.1             | VDD_MON Example Settings                      | 7 |  |  |  |  |

|     | 5.3                            | VSYS P            | ower-up                                       | 8 |  |  |  |  |

| 6   | Monit                          | toring Ou         | Itput Voltages                                | 9 |  |  |  |  |

|     | 6.1                            | PWR_O             | К                                             | 9 |  |  |  |  |

|     |                                | 6.1.1             | PWR_OK Example Settings 1                     | 0 |  |  |  |  |

|     |                                | 6.1.2             | Interrupt Asserted by PWR_OK and nIRQ 1       | 1 |  |  |  |  |

|     | 6.2                            | nRESET            | <sup>.</sup>                                  | 1 |  |  |  |  |

|     |                                | 6.2.1             | nRESET Example Settings1                      | 1 |  |  |  |  |

|     | 6.3                            | REG_U             | /OV, nIRQ 1                                   | 2 |  |  |  |  |

|     |                                | 6.3.1             | REG_UVOV, nIRQ Example Settings 1             | 2 |  |  |  |  |

|     | 6.4                            | Manual I          | Neasurement of Regulator Output Voltages1     | 3 |  |  |  |  |

|     |                                | 6.4.1             | Example of Manual Voltage Read 1              | 4 |  |  |  |  |

| 7   | 7 Monitoring External Voltages |                   |                                               |   |  |  |  |  |

|     | 7.1                            | 7.1 COMP1V2, nIRQ |                                               |   |  |  |  |  |

|     |                                | 7.1.1             | COMP1V2 Example Settings 1                    |   |  |  |  |  |

# **Figures**

| Figure 1: Signals and Registers used for Voltage Monitoring | . 5 |

|-------------------------------------------------------------|-----|

| Figure 2: VSYS Monitoring                                   | . 6 |

| Figure 3: VDD_MON Event                                     |     |

| Figure 4: VDD_MON Debouncing                                |     |

| Figure 5: VSYS Power-up                                     | . 8 |

| Figure 6: Interrupt Asserted by PWR_OK and nIRQ             | 11  |

| Figure 7: COMP1V2 Comparator                                |     |

| •                                                           |     |

# **Tables**

| Table 1: Signal Descriptions                                        | 5    |

|---------------------------------------------------------------------|------|

| Table 2: Event Descriptions                                         |      |

| Table 3: Example Settings for VDD_MON Voltage Detection             | 7    |

| Table 4: Assignment of Regulators for Voltage Monitoring            | 9    |

| Table 5: Example Settings for LDO1 and IO Buck Output Monitoring    | . 10 |

| Table 6: LDO1 Exceeding the Upper Limit                             | . 10 |

| Table 7: Example Settings for LDO3 Output Monitoring                | . 11 |

| Table 8: LDO3 Exceeding the Upper Limit                             | . 12 |

| Table 9: Example Settings for LDO2 and CORE1 Buck Output Monitoring | . 12 |

| Table 10: LDO2 Exceeding the Upper Limit                            | . 13 |

| Table 11: ADC Channel Addressing                                    | . 13 |

| Table 12: Read Buck CORE1 Voltage                                   |      |

| Table 13: Read LDO3 Voltage                                         |      |

| Table 14: Example Settings for COMP1V2 Comparator                   |      |

## **1** Terms and Definitions

LDO

Low DropOut voltage regulator. Used in battery operated systems, where the output voltage is typically lower than the input voltage.

PMIC Power Management Integrated Circuits. Integrated circuits for managing power requirements of the host system.

## 2 References

[1] DA9063, Datasheet, Dialog Semiconductor.

# 3 Introduction

The monitoring of input and output voltages on a PMIC is valuable for most applications. The range of signals and internal events described in this document allows Dialog's DA9063 to provide many opportunities to indicate and handle input/output out-of-range conditions.

# 4 Signals and Registers Overview

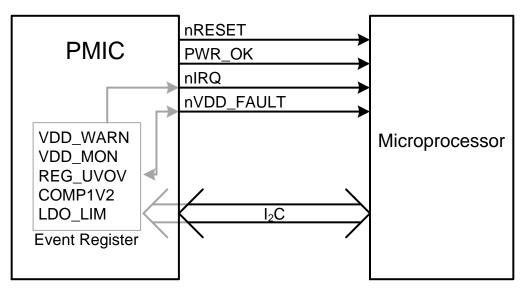

DA9063 provides several signals and internal events to help monitor input voltage VSYS and output voltages (bucks and LDOs).

Figure 1: Signals and Registers used for Voltage Monitoring

#### Table 1: Signal Descriptions

| Signal     | Description                                                                                                      |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| PWR_OK     | Out-of-range output detection via ADC (LDOs and bucks).                                                          |  |  |  |

| nIRQ       | Indicates that an interrupt event has occurred and that event information is available in the related registers. |  |  |  |

| nVDD_FAULT | Indicates a supply voltage (VSYS) low status.                                                                    |  |  |  |

| nRESET     | Asserted if microprocessor enters the RESET state.                                                               |  |  |  |

#### **Table 2: Event Descriptions**

| Event    | Description                                                    |

|----------|----------------------------------------------------------------|

| VDD_WARN | VSYS dropped below VDD_FAULT_UPPER threshold.                  |

| VDD_MON  | VSYS crossed VSYS_MON threshold.                               |

| REG_UVOV | Regulator output underflow or overflow.                        |

| COMP1V2  | 1.2 V comparator (ADC channel 2) state changed.                |

| LDO_LIM  | LDO3, 4, 7, 8 or 11 current limit exceeded for more than 10 ms |

# 5 VSYS Monitoring

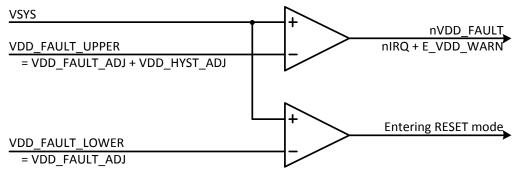

The system supply voltage, VSYS, is monitored with two comparators as shown in Figure 2.

Figure 2: VSYS Monitoring

## 5.1 VSYS Under-Voltage, E\_VDD\_WARN, nIRQ and nVDD\_FAULT

The first comparator monitors the higher voltage threshold, VDD\_FAULT\_UPPER. Whenever VSYS voltage goes below VDD\_FAULT\_UPPER, the system issues the warning E\_VDD\_WARN and sets nIRQ low (unless it is masked), so the system can run safety routines, backup data and power-down securely. Simultaneously, nVDD\_FAULT (available on GPIO12) goes low. E\_VDD\_WARN and nIRQ output can be de-asserted at any time during the under-voltage condition. The nVDD\_FAULT output is strictly driven by the comparator. Its type is push-pull only and active level is selected by GPIO12\_MODE: active-low (0) or active-high (1). The nIRQ output is either active-low push-pull (PM\_O\_TYPE = 0) or active-low open-drain (PM\_O\_TYPE = 1) and can be supplied from either VDD\_IO1 (PM\_O\_V = 0) or VDD\_IO2 (PM\_O\_V = 1).

The second comparator monitors the lower voltage threshold, VDD\_FAULT\_LOWER. Whenever VSYS voltage goes below VDD\_FAULT\_LOWER, the PMIC enters RESET mode.

Both thresholds (VDD\_FAULT\_UPPER and VDD\_FAULT\_LOWER) are adjustable by OTP configurable register CONFIG\_B. VDD\_FAULT\_LOWER is set directly by VDD\_FAULT\_ADJ in the register from 2.5 V to 3.25 V in 50 mV steps. VDD\_FAULT\_UPPER is set indirectly by VDD\_HYST\_ADJ (VDD\_FAULT\_UPPER = VDD\_FAULT\_ADJ + VDD\_HYST\_ADJ).

VDD\_HYST\_ADJ hysteresis is adjustable from 100 mV to 450 mV in 50 mV steps.

## 5.2 VDD\_MON, nIRQ

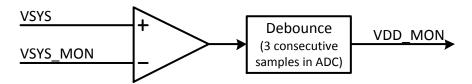

The VDD\_MON event is detected based on a comparison of the supply voltage VSYS and the VSYS\_MON threshold as shown in Figure 3.

#### Figure 3: VDD\_MON Event

VDD\_MON is asserted whenever the VSYS voltage value in ADC exceeds or drops below the adjustable threshold VSYS\_MON for three consecutive samples, see Figure 4. nIRQ is asserted simultaneously with VDD\_MON (unless it is masked). This provides a 'power good' signal to trigger boot activity on the microprocessor.

After the nIRQ assertion, the automatic measurement of channel VSYS is paused for reading. The event causing the voltage value is kept inside the result register, VSYS\_RES. The host has to clear the VDD\_MON flag to re-enable the supervision of VSYS.

| Application Note | Revision 2.3 | 24-Nov-2016 |

|------------------|--------------|-------------|

|                  |              |             |

Figure 4: VDD\_MON Debouncing

VSYS\_MON threshold can be adjusted by setting the VSYS\_MON register, the range is from 2.5 V (VSYS\_MON = 0x00h) to 5.5 V (VSYS\_MON = 0xFFh). VSYS auto measurements must be enabled (AUTO\_VSYS\_EN = 1).

VDD\_MON output is push-pull type and can be either active low (GPIO12\_MODE = 0) or active high (GPIO12\_MODE = 1).

The nIRQ output is either active-low push-pull (PM\_O\_TYPE = 0) or active-low open-drain (PM\_O\_TYPE = 1) and can be supplied from either VDD\_IO1 (PM\_O\_V = 0) or VDD\_IO2 (PM\_O\_V = 1).

#### 5.2.1 VDD\_MON Example Settings

Before proceeding, clear all interrupt events (ensure the nIRQ output is high).

| Setting            | Description                                        |

|--------------------|----------------------------------------------------|

| AUTO_VSYS_EN = 1   | VSYS auto measurements enabled.                    |

| VSYS_MON = 0x44h   | VSYS_MON threshold is set to 3.3 V.                |

| GPIO12_PIN = 0x02h | Output is controlled by the state of VSYS monitor. |

| GPIO12_MODE = 0    | Output is active-low push-pull type.               |

#### Table 3: Example Settings for VDD\_MON Voltage Detection

A VDD\_MON event is asserted as soon as three consecutive samples under or over VDD\_MON thresholds are recognized. The nIRQ output is asserted simultaneously with VDD\_MON (unless it is masked). The voltage value that triggered the event is stored in the result register, VSYS\_RES (VSYS\_RES = 0x00h is equal to VSYS = 2.5 V; VSYS\_RES = 0xFFh is equal to VSYS = 5.5 V).

## 5.3 VSYS Power-up

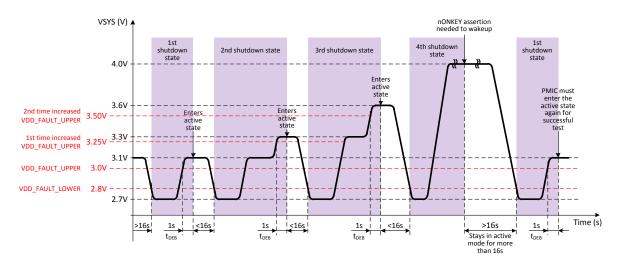

VSYS monitoring contains additional mechanisms to prevent an application starting from a weak power supply, example voltages are shown in Figure 5.

#### Figure 5: VSYS Power-up

If DA9063 is started and the VSYS voltage drops below the VDD\_FAULT\_LOWER threshold (possibly because of a high load), it enters SHUTDOWN state. Next time it starts, VSYS has to go above VDD\_FAULT\_UPPER + 0.25 V in order to enter the ACTIVE state. If VSYS drops below VDD\_FAULT\_LOWER again, the next time it has to cross VDD\_FAULT\_UPPER + 0.50 V. The VDD\_FAULT\_UPPER threshold is not further increased. The timeout for voltage drop is 16 s (the voltage has to drop within 16 s) so the VDD\_FAULT\_UPPER threshold is increased after the next start up. DA9063 also cannot enter an ACTIVE state before t<sub>DEB</sub> debounce time expires (typically 1 s) after crossing the appropriate threshold, see Figure 5.

# 6 Monitoring Output Voltages

## 6.1 PWR\_OK

PWR\_OK becomes active if none of the selected regulators are out-of-range. It is available through the GP\_FB2 pin, when PM\_FB2\_PIN = 0 and the REG\_UVOV interrupt is masked (M\_REG\_UVOV = 1). Monitored regulator outputs must be enabled, otherwise the out-of-range condition is detected. In the case where at least one of the supervised regulators is out-of-range or a monitored regulator output is disabled, the PWR\_OK signal becomes inactive. There are also five special cases for the PWR\_OK:

- If the supply monitoring is disabled, so that none of the supplies are monitored, the PWR\_OK becomes inactive.

- The output voltage monitoring is not available for BUCKPRO in the DDR memory termination mode.

- When BUCKCORE1, BUCKCORE2 and BUCKMEM, BUCKIO are configured in merged mode only the master buck should be monitored. BUCKCORE1 and BUCKMEM are the master bucks.

- The GPIO4 pin should be configured as the remote feedback for BUCKCORE1 and BUCKCORE2 in merged mode because the GP\_FB2 pin is needed for PWR\_OK.

- If any of the monitored LDOs are configured in bypass mode, the PWR\_OK becomes inactive.

If any regulator is out-of-range, its ID is stored in MON\_A8\_IDX, MON\_A9\_IDX, or MON\_A10\_IDX, see Table 4. The last voltage measurement from the MON\_A8\_IDX group is stored in MON1\_RES, from the MON\_A9\_IDX group in MON2\_RES and from the MON\_A10\_IDX group in MON3\_RES.

| Register<br>Address | Bit | Туре | Label      | Default | Description                                                                                                                                                       |

|---------------------|-----|------|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x118               | 7   | R    | Reserved   | 0       |                                                                                                                                                                   |

| MON_REG_5           | 6:4 | R    | MON_A9_IDX | 000     | Latest measurement at channel A9 was:<br>000: none<br>001: BUCKIO<br>010: BUCKMEM<br>011: BUCKPERI<br>100: LDO1<br>101: LDO2<br>101: LDO5<br>> 110: reserved      |

|                     | 3   | R    | Reserved   | 0       |                                                                                                                                                                   |

|                     | 2:0 | R/W  | MON_A8_IDX | 000     | Latest measurement at channel A8 was:<br>000: none<br>001: BUCKCORE1<br>010: BUCKCORE2<br>011: BUCKPRO<br>100: LDO3<br>101: LDO4<br>110: LDO11<br>> 110: reserved |

| 0x119               | 7   | R    | Reserved   | 0       |                                                                                                                                                                   |

| MON_REG_6           | 6:4 | R    | Reserved   | 000     |                                                                                                                                                                   |

|                     | 3   | R    | Reserved   | 0       |                                                                                                                                                                   |

| Register<br>Address | Bit | Туре | Label       | Default | Description                                                                                                                             |

|---------------------|-----|------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

|                     | 2:0 | R    | MON_A10_IDX | 000     | Latest measurement at channel A10 was:<br>000: none<br>001: LDO6<br>010: LDO7<br>011: LDO8<br>100: LDO9<br>101: LD10<br>> 101: reserved |

PWR\_OK is either active-low push-pull ( $GP_FB2_TYPE = 0$ ) or active-high open-drain ( $GP_FB2_TYPE = 1$ ). The active-low push-pull is chosen to avoid permanently draining current through a pull resistor while the system is active.

#### 6.1.1 **PWR\_OK Example Settings**

Before proceeding, clear all interrupt events (ensure the nIRQ output is high).

| Setting           | Description                                                                                                 |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| M_REG_UVOV = 1    | Mask bit for REG_UVOV must be set to enable PWR_OK functionality.                                           |  |  |  |  |

| $PM_FB2_PIN = 0$  | GP_FB2 output has PWR_OK functionality.                                                                     |  |  |  |  |

| GP_FB2_TYPE = 0   | Active-low output. GP_FB2 is low if outputs are within range. GP_FB2 is high if any output is out-of-range. |  |  |  |  |

| MON_MODE = 0x00h  | UV/OV event when out-of-range                                                                               |  |  |  |  |

| MON_DEB = 1       | Debouncing on                                                                                               |  |  |  |  |

| MON_THRES = 0x00h | Monitored output threshold accuracy is ±25 %.                                                               |  |  |  |  |

| $VLDO1_A = 0x14h$ | LDO1_A voltage is 1.0 V.                                                                                    |  |  |  |  |

| VLDO1_SEL = 0     | LDO1_A voltage is on LDO1 output.                                                                           |  |  |  |  |

| LDO1_EN = 1       | LDO1 output enabled.                                                                                        |  |  |  |  |

| VBIO_A = 0x0Ah    | BIO_A voltage is 1.0 V.                                                                                     |  |  |  |  |

| VBIO_SEL = 0      | BIO_A voltage is on BIO output.                                                                             |  |  |  |  |

| BIO_EN = 1        | BUCKIO output enabled.                                                                                      |  |  |  |  |

| LDO1_MON_EN = 1   | Monitoring of LDO1 output voltage enabled.                                                                  |  |  |  |  |

| BIO_MON_EN = 1    | Monitoring of BUCKIO output voltage enabled.                                                                |  |  |  |  |

| Table 5: Exam | ple Settinas f | or LDO1 a | and IO Buck | Output Monitoring |

|---------------|----------------|-----------|-------------|-------------------|

| Tuble of Exam | pio oouingo i  |           |             | output monitoring |

Both LDO1 and VBIO voltages are monitored for minimum voltage 0.75 V (1.0 V - 25 % = 1.0 V \* 0.75) and maximum voltage 1.25 V (1.0 V + 25 % = 1.0 V \* 1.25). If any of these thresholds are exceeded, PWR\_OK output is de-asserted.

If LDO1 exceeds the upper limit (1.25 V), the settings in Table 6 are performed.

#### Table 6: LDO1 Exceeding the Upper Limit

| Setting            | Description                                                                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| E_REG_UVOV = 1     | PMIC detected under-voltage or over-voltage condition.                                                                                                 |

| LDO1_EN = 1        | LDO1 output <b>stays</b> enabled.                                                                                                                      |

| MON_A9_IDX = 0x04h | Out-of-range condition detected on LDO2.                                                                                                               |

| MON2_RES = 0x42h   | Last output voltage before out-of-range detection. It should be higher than 0x3Fh (1.25 V). 0x00h corresponds to 0.0 V and 0xFFh corresponds to 5.0 V. |

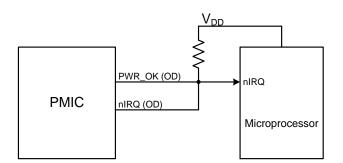

#### 6.1.2 Interrupt Asserted by PWR\_OK and nIRQ

If the configuration for PWR\_OK output is used, the REG\_UVOV mask bit must be set (M\_REG\_UVOV = 1) and nIRQ is not asserted if an out-of-range condition is detected. If the interrupt should still be detected, it is possible to set both outputs (nIRQ and PWR\_OK) as open-drain and connect them together, see Figure 6.

Open-drain settings:

GP\_FB2\_TYPE = 1 PWR\_OK is active-high open-drain output type.

PM\_O\_TYPE = 1 nIRQ is active-low open-drain output type.

Figure 6: Interrupt Asserted by PWR\_OK and nIRQ

#### 6.2 nRESET

nRESET is asserted to force the microprocessor to enter the RESET state. In order to activate assertion of nRESET during an out-of-range condition, both MON\_RES and M\_REG\_UVOV mask bits must be set high. Minimum assertion time is 1 ms.

nRESET is always asserted at the beginning of a DA9063 cold start from NO POWER / DELIVERY / RTC mode. It is asserted in ACTIVE mode before DA9063 starts powering down to RESET mode (triggered from user, host, or an error condition).

The nRESET signal is de-asserted following the expiry of the RESET\_TIMER. The trigger for the RESET\_TIMER is programmable by the OTP from EXT\_WAKEUP, SYS\_UP, PWR\_UP, or leaving PMIC RESET state. The duration of the RESET\_TIMER is programmable from 1 ms to 1 s. This flexibility allows the RESET functionality to be optimized for any host system.

nRESET can be asserted directly by setting FORCE\_RESET signal (FORCE\_RESET = 1).

The nRESET output is either active-low push-pull (PM\_O\_TYPE = 0) or active-low open-drain (PM\_O\_TYPE = 1). The nRESET can be supplied either from VDD\_IO1 (PM\_O\_V = 0) or from VDD\_IO2 (PM\_O\_V = 1).

#### 6.2.1 nRESET Example Settings

| Setting           | Description                                                                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| M_REG_UVOV = 1    | Mask bit for REG_UVOV must be set to enable PWR_OK functionality.                                                                                  |

| MON_MODE = 0x00h  | UV/OV event when out-of-range.                                                                                                                     |

| MON_DEB = 1       | Debouncing on.                                                                                                                                     |

| MON_RES = 1       | nRESET output asserted if out-of-range condition is detected. The following registers <b>must</b> be set $M_REG_UVOV = 1$ and $MON_MODE = 0x00h$ . |

| MON_THRES = 0x00h | Monitored output threshold accuracy is ±25 %.                                                                                                      |

| VLDO3_A = 0x05h   | LDO3_A voltage is 1.0 V.                                                                                                                           |

| VLDO3_SEL = 0     | LDO3_A voltage is on LDO3 output.                                                                                                                  |

#### Table 7: Example Settings for LDO3 Output Monitoring

```

Application Note

```

| Setting         | Description                                |

|-----------------|--------------------------------------------|

| LDO3_EN = 1     | LDO3 output enabled.                       |

| LDO3_MON_EN = 1 | Monitoring of LDO3 output voltage enabled. |

LDO3 output is monitored for minimum voltage 0.75 V (1.0 V - 25 % = 1.0 V \* 0.75) and maximum voltage 1.25 V (1.0 V + 25 % = 1.0 V \* 1.25). If any of these thresholds are exceeded, the nRESET output is asserted.

If LDO3 exceeds the upper limit (1.25 V), the settings in Table 8 are performed.

| Setting            | Description                                                                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| E_REG_UVOV = 1     | PMIC detected under-voltage or over-voltage condition.                                                                                               |

| LDO3_EN = 1        | LDO3 output stays enabled.                                                                                                                           |

| MON_A8_IDX = 0x04h | Out-of-range condition detected on LDO3.                                                                                                             |

| MON2_RES = 0x42h   | Last output voltage before out-of-range detection. It should be higher than 0x3Fh (1.25 V). 0x00 corresponds to 0.0 V and 0xFF corresponds to 5.0 V. |

## 6.3 **REG\_UVOV**, **nIRQ**

If any regulator is out-of-range, the REG\_UVOV event is asserted. Its ID is stored in MON\_A8\_IDX / MON\_A9\_IDX / MON\_A10\_IDX and the last voltage measurements are stored in MON1\_RES / MON2\_RES / MON3\_RES, see Table 4. At the same time as the REG\_UVOV event, the nIRQ output is asserted.

Out-of-range can be adjusted in MON\_THRES ranging from 3.125 % to 25 %.

The nIRQ output is either active-low push-pull (PM\_O\_TYPE = 0) or active-low open-drain (PM\_O\_TYPE = 1) and can be supplied from either VDD\_IO1 (PM\_O\_V = 0) or VDD\_IO2 (PM\_O\_V = 1).

## 6.3.1 REG\_UVOV, nIRQ Example Settings

Clear all interrupt events (nIRQ output is high).

Table 9: Example Settings for LDO2 and CORE1 Buck Output Monitoring

| Setting           | Description                                                       |

|-------------------|-------------------------------------------------------------------|

| M_UVOV_MASK = 0   | Mask bit for REG_UVOV must be set to enable PWR_OK functionality. |

| PM_O_TYPE = 0     | nIRQ output is active-low push-pull type.                         |

| PM_O_V = 0        | nIRQ is supplied from VDD_IO1.                                    |

| MON_MODE = 0x00h  | UV/OV event when out-of-range.                                    |

| MON_DEB = 1       | Debouncing on.                                                    |

| MON_THRES = 0x00h | Monitored output threshold accuracy is ±25 %.                     |

| VLDO2_A = 0x14h   | LDO2_A voltage is 1.0 V.                                          |

| VLDO2_SEL = 0     | LDO2_A voltage is on LDO2 output.                                 |

| LDO2_EN = 1       | LDO2 output enabled.                                              |

| VBCORE2_A = 0x46h | BCORE2_A voltage is 1.0 V.                                        |

| VBCORE2_SEL = 0   | BCORE2_A voltage is on BIO output.                                |

| BCORE2_EN = 1     | BCORE2 buck output enabled.                                       |

| LDO2_MON_EN = 1   | Monitoring of LDO2 output voltage enabled.                        |

| Setting           | Description                                       |

|-------------------|---------------------------------------------------|

| BCORE2_MON_EN = 1 | Monitoring of BCORE2 buck output voltage enabled. |

Both LDO2 and VBCORE2 voltages are monitored for minimum voltage 0.75 V (1.0 V - 25 % = 1.0 V \* 0.75) and maximum voltage 1.25 V (1.0 V + 25 % = 1.0 V \* 1.25). If any of these thresholds are exceeded, E\_REG\_UVOV event bit is set and the nIRQ output is asserted. Also the regulator output, which exceeded the limit, is disabled.

If LDO2 exceeds the upper limit (1.25 V), the settings in Table 10 are performed.

| Setting            | Description                                                                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| E_REG_UVOV = 1     | PMIC detected under-voltage or over-voltage condition.                                                                                                 |

| LDO2_EN = 0        | LDO2 output disabled.                                                                                                                                  |

| MON_A9_IDX = 0x05h | Out-of-range condition detected on LDO2.                                                                                                               |

| MON2_RES = 0x42h   | Last output voltage before out-of-range detection. It should be higher than 0x3Fh (1.25 V). 0x00h corresponds to 0.0 V and 0xFFh corresponds to 5.0 V. |

#### Table 10: LDO2 Exceeding the Upper Limit

nIRQ output is asserted (goes low).

## 6.4 Manual Measurement of Regulator Output Voltages

In addition to the automatic output voltage monitoring, the DA9063 also provides functionality to allow the host to make a manual measurement of the output voltage, of any of the enabled regulators, using the integrated ADC.

The key to all manual measurements using the DA9063 ADC is that the results are always returned in the ADC\_RES registers ADC\_RES\_H, (0x38) and ADC\_RES\_L (0x37). ADC\_RES\_H contains the upper eight bits of the 10 bit result. ADC\_RES\_L bits 7:6 contain the two LSBs.

The 17 regulator outputs are split between three channels of the ADC. For the channel allocation, see Table 11.

To perform a manual measurement, both the ADC channel and the individual regulator index must be specified. The regulator index is written to the MON\_Ax\_IDX value in register MON\_REG\_5 (0x11E) or MON\_REG\_6 (0x11F). The ADC channel is selected by setting the ADX\_MUX value, ADC\_MAN[3:0].

Once both the ADC channel and the regulator index have been specified the manual measurement is triggered by writing a '1' to bit 4 of ADC\_MAN,(0x34).

Note that bit 4 of ADC\_MAN is a self-clearing bit and is cleared to indicate that the measurement is complete. Event E\_ADC\_RDY in register EVENT\_A,(0x06) is also asserted to indicate that the measurement is compete and that the result is available to be read.

For more information about the ADC functionality, see the DA9063 datasheet [1].

The REG\_RANGE ADC channels have a range of 0 V to 5 V. For the 10 bit manual measurements each LSB represents 4.883 mV.

| ADC Channel                         | Select Register | Regulator | Index |

|-------------------------------------|-----------------|-----------|-------|

| REG_RANGE1<br>ADX_MUX[3:0] = 0x1000 | MON_A8_IDX      | BUCKCORE1 | 1     |

| ADA_MOA[3.0] = 0x1000               |                 | BUCKCORE2 | 2     |

|                                     |                 | BUCKPRO   | 3     |

#### Table 11: ADC Channel Addressing

| ADC Channel           | Select Register | Regulator | Index |

|-----------------------|-----------------|-----------|-------|

|                       |                 | LDO3      | 4     |

|                       |                 | LDO4      | 5     |

|                       |                 | LDO11     | 6     |

| REG_RANGE2            | MON_A9_IDX      | вискіо    | 1     |

| ADX_MUX[3:0] = 0x1001 |                 | BUCKMEM   | 2     |

|                       |                 | BUCKPERI  | 3     |

|                       |                 | LDO1      | 4     |

|                       |                 | LDO2      | 5     |

|                       |                 | LDO5      | 6     |

| REG_RANGE3            | MON_A9_IDX      | LDO6      | 1     |

| ADX_MUX[3:0] = 0x1010 |                 | LDO7      | 2     |

|                       |                 | LDO8      | 3     |

|                       |                 | LDO9      | 4     |

|                       |                 | LDO10     | 5     |

#### 6.4.1 Example of Manual Voltage Read

This section provides the details of how to perform the manual read.

For this example, BUCKCORE1 is set to 0.9 V and LDO3 is set to 1.2 V, and both regulators are already enabled.

Both BUCKCORE1 and LDO3 are assigned to ADC channel REG\_RANGE1. The REG\_RANGE1 select register is MON\_REG\_5:MON\_A8\_IDX.

BUCKCORE1 is index 1 on channel REG\_RANGE1.

LDO3 is index 4 on channel REG\_RANGE1.

#### Table 12: Read BUCKCORE1 Voltage

| Setting          | Description                                |

|------------------|--------------------------------------------|

| ADC_MUX[3:0]= 8h | Select ADC channel REG_RANGE1              |

| MON_A8_IDX = 0h  | Select BUCKCORE1                           |

| ADC_MAN = 1      | Trigger the manual conversion              |

|                  | Read the result from ADC_RES_H & ADC_RES_L |

$ADC_RES_H = 0x2E$

ADC\_RES\_L=0x40

This results in a 10 bit value of 0010111001b =0x0B9 = 185dec.

The measured voltage is 185 \* 4.883 mV = 0.903 V.

| Application Note | Revision 2.3 |

|------------------|--------------|

|------------------|--------------|

## Table 13: Read LDO3 Voltage

| Setting           | Description                                |

|-------------------|--------------------------------------------|

| ADC_MUX[3:0]= 0x8 | Select ADC channel REG_RANGE1              |

| MON_A8_IDX = 0x4  | Select LDO3                                |

| ADC_MAN = 1       | Trigger the manual conversion              |

|                   | Read the result from ADC_RES_H & ADC_RES_L |

$ADC_RES_H = 0x3D$

ADC\_RES\_L=0x80

This results in a 10 bit value of 0011110110b = 0x0F6 = 246dec.

The measured voltage is 246 \* 4.883 mV = 1.201 V.

# 7 Monitoring External Voltages

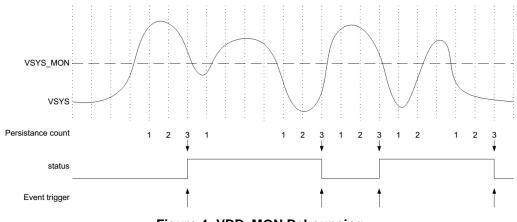

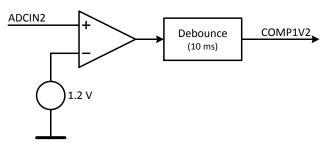

## 7.1 COMP1V2, nIRQ

A comparator with a threshold of 1.2 V is connected to the input of ADC channel 2, see Figure 7. The comparator is asserted whenever the input voltage exceeds or falls below 1.2 V for at least 10 ms (debouncing) after being enabled in COMP1V2\_ENA. Status flag COMP1V2 is indicating the actual state and a maskable interrupt request E\_COMP1V2 is generated at falling and rising edge state transitions. The user can disable the comparator in COMP1V2\_EN when auto measurements with high resolution are executed on ADCIN2.

Figure 7: COMP1V2 Comparator

#### 7.1.1 COMP1V2 Example Settings

Before proceeding clear all interrupt events (ensure the nIRQ output is high).

#### Table 14: Example Settings for COMP1V2 Comparator

| Setting         | Description                                 |

|-----------------|---------------------------------------------|

| GPIO1_PIN=0x00h | GPIO1 is used as an input of ADC channel 2. |

| COMP1V2_EN=1    | COMP1V2 comparator is enabled.              |

Whenever the voltage on ADCIN2 input goes above or below 1.2 V for at least 10 ms, COMP1V2 event is detected and the nIRQ output is asserted (unless it is masked).

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2016 Dialog Semiconductor. All rights reserved.

# **Contacting Dialog Semiconductor**

United Kingdom (Headquarters) Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

#### The Netherlands

Dialog Semiconductor B.V. Phone: +31 73 640 8822 Email:

enquiry@diasemi.com

# Application Note

#### North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japan

Dialog Semiconductor K. K. Phone: +81 3 5425 4567

#### Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222 Web site:

Web site: www.dialog-semiconductor.com

#### Singapore

Dialog Semiconductor Singapore Phone: +65 64 8499 29

#### Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 3769 5200

#### Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200

#### China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

#### China (Shanghai) Dialog Semiconductor China Phone: +86 21 5424 9058

CFR0014

**Revision 2.3**

24-Nov-2016