# **Application Note**

## Using Dialog's Integrated Power Switches in Super Capacitor Applications

**AN-CM-246**

### Abstract

This application note describes some common problems caused by powering up on high capacitive loads. Using Dialog Integrated Power Switches it is easy to power up from very small capacitance to relatively high value super capacitors.

## Contents

| Ab  | stract                                 | . 1 |

|-----|----------------------------------------|-----|

| Co  | ntents                                 | 2   |

| Fig | jures                                  | 2   |

| 1   | Terms and Definitions                  | 3   |

| 2   | References                             | 3   |

| 3   | Introduction                           | 4   |

| 4   | Design Description                     | 5   |

| 5   | Start-up Inrush Current Considerations | 6   |

| 6   | Capacitive Load Operation              | 7   |

| 7   | Conclusion                             | 9   |

| Re  | vision History1                        | 10  |

## **Figures**

| 4 |

|---|

| 5 |

| 5 |

| 6 |

|   |

| 7 |

|   |

|   |

| 8 |

|   |

| 9 |

|   |

© 2018 Dialog Semiconductor

#### **1** Terms and Definitions

| ACL | Active Current Limit |

|-----|----------------------|

|     |                      |

IC Integrated Circuit

IPS Integrated Power Switch

PCB Printed Circuit Board

### 2 References

- [1] SLG59M1717V, Datasheet, Dialog Semiconductor.

- [2] AN-1068, GFET3 and HFET1 Integrated Power Switch Basics, Application Note, Dialog Semiconductor.

Author: Andrii Hrypa and Petro Zeykan

### 3 Introduction

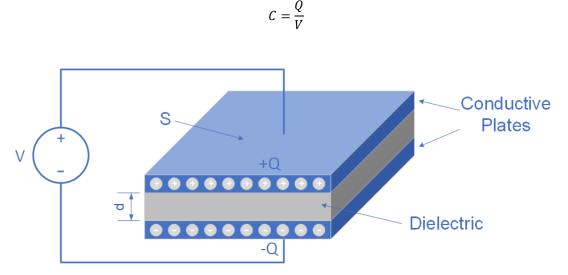

Capacitance is the ability of a system to store an electric charge (Figure 1). Capacitance value is the ratio of the charge accumulated on conductive plates to the applied voltage:

#### Figure 1: Two Charged Conductive Plates Separated with Dielectric Layer

The capacitance of a parallel plate system is proportional to the plate area S and inversely proportional to the distance *d* between these two conductive plates.

$$C = \frac{\varepsilon S}{d} \tag{1}$$

where

$\varepsilon$  - an absolute permittivity of the dielectric material;

*S* - a square of conductive plate;

*d* - a distance between two conductive plates.

A component designed to store electric charge is called capacitor. In electronic circuits, capacitors can be used in a variety of different ways: coupling and decoupling effects, smoothing output signal of rectifiers, as a timing element, etc.

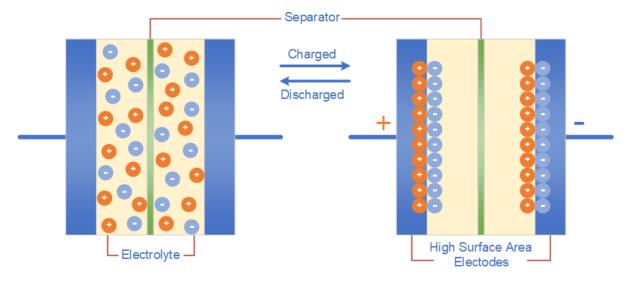

A capacitor which can store a great amount of charge is called a supercapacitor or ultracapacitor. Supercapacitor's electrodes are made of the materials that have a high surface area. This allows to hold much more charge without increasing capacitor's size.

Supercapacitors have an electrolyte inside and when the electrodes are charged, the electrolyte polarizes according to the charge of the electrodes (Figure 2). This charge separation creates two oppositely charged layers. Such system behaves like two conventional capacitors attached in series. These capacitors have plate separation distances that are a few nanometers thick.

| Anı | olica | atior | NO <sup>t</sup> | te |

|-----|-------|-------|-----------------|----|

|     |       |       |                 |    |

**Revision 1.0**

#### Figure 2: A Supercapacitor Structure and Charge Distribution

The combination of the increased surface area and the small plate separation distance increases the capacitance and the energy stored in the supercapacitor.

## 4 Design Description

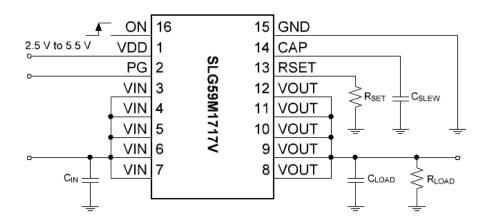

In this application note, we will describe how to apply Dialog's nFET SLG59M1717V IPS to power up into super-capacitor or very high capacitive loads. To implement a very large capacitive load, (3) 5 V, 0.22 F supercapacitors were connected in parallel. The SLG59M1717V is a high-performance, 4 m $\Omega$ , 5 A single-channel, feature-rich nFET IPS designed for all 0.8 V to 5.5 V power rail applications. In addition to its world-class RDS<sub>ON</sub>, the SLG59M1717V incorporates two-stage overcurrent protection: (1) resistor-adjustable Active Current Limit and (2) a fixed 1.6 A Short-circuit Current Limit.

A typical connection of Dialog's SLG59M1717V in capacitive/resistive load applications is illustrated in Figure 3.

Figure 3: Typical Application Diagram of SLG59M1717V

**Application Note**

**Revision 1.0**

## 5 Start-up Inrush Current Considerations

When a voltage is applied to a discharged (or an uncharged) capacitor, a large initial current may flow through an IPS. This current is called inrush current and can be calculated by equation below:

Inrush Current,  $I = C \frac{dV}{dt}$

where

C - is the total load capacitance;

$\frac{dV}{dt}$  - the IPS's V<sub>OUT</sub> slew rate during voltage ramp up.

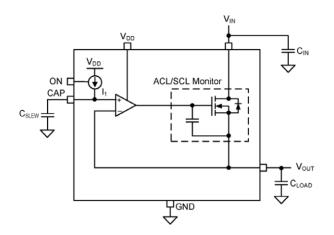

To reduce inrush current for a given load capacitance, it is necessary to decrease the IPS's  $V_{OUT}$  slew rate. An equivalent circuit of the SLG59M1717V's slew rate control loop with capacitors at its VIN and VOUT pins is shown in Figure 4:

For a desired V<sub>OUT</sub> slew rate (V<sub>OUT(SR)</sub>), a corresponding C<sub>SLEW</sub> value is selected. At the VOUT pin and with ON = LOW, the internal FET is OFF, V<sub>OUT</sub> is initially at 0 V, and there is no stored charge on C<sub>LOAD</sub>. When a low-to-high transition is applied to the IC's ON pin, an internal current source (I<sub>1</sub>) is enabled which, in turn, charges the external slew rate capacitor, C<sub>SLEW</sub>. The SLG59M1717V's internal micropower op amp sets the circuit's V<sub>OUT(SR</sub>) based on the slew rate of the nodal voltage at its noninverting pin (the voltage at the CAP pin).

| Application Note Revision 1.0 03-Jul-2 |                  |              |             |

|----------------------------------------|------------------|--------------|-------------|

|                                        | Application Note | Revision 1.0 | 03-Jul-2018 |

## 6 Capacitive Load Operation

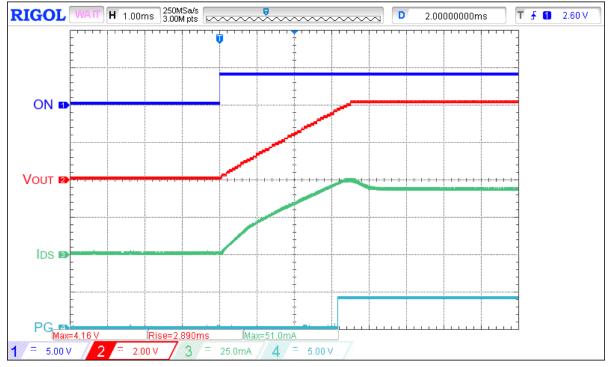

In Figure 5, a typical SLG59M1717's power up behavior for resistive and capacitive load is illustrated. As can be observed, output voltage and current through the IPS are changing linearly.

Figure 5: Typical Power up Operation Waveform for  $V_{DD} = V_{IN} = 4 V$ ,  $R_{SET} = 40 k\Omega$ ,  $C_{SLEW} = 10 nF$ ,

$R_{LOAD} = 100 \ \Omega, \ C_{LOAD} = 10 \ \mu F$

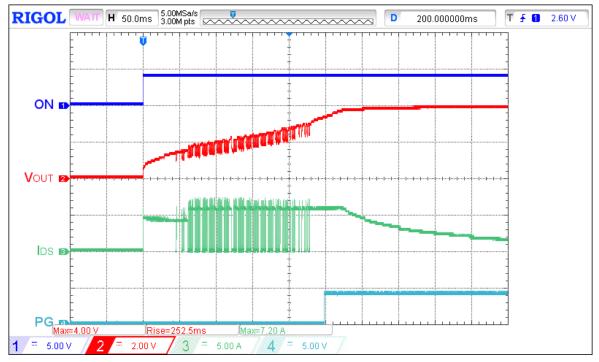

In this example, a 10 nF  $C_{SLEW}$  capacitor sets the slew rate to approximately 1.1 V/ms, thus inrush current is only 11 mA. In using a 0.66F supercapacitor, the resultant inrush current is dramatically increased and a non-linear ramp is observed during power up (see Figure 6). Since the inrush current is higher than the IPS's I<sub>ACL</sub> threshold (set by external R<sub>SET</sub> resistor), the IPS's internal overcurrent protection is activated. To keep the load capacitor's charging current from exceeding the IPS's I<sub>ACL</sub> threshold, the ACL monitor increases the FET resistance. However, if the overload condition persists where the die temperature rises because of the increased FET resistance, the IPS's internal Thermal Shutdown Protection circuit will be activated. If the die temperature exceeds 150 °C the IPS's internal Thermal Shutdown Protection circuit shuts the FET completely OFF, thereby allowing the die to cool. When the die cools to the IPS's lower 130 °C temperature threshold, the FET is automatically turned back on. This process may repeat as long as the output current overload condition persists.

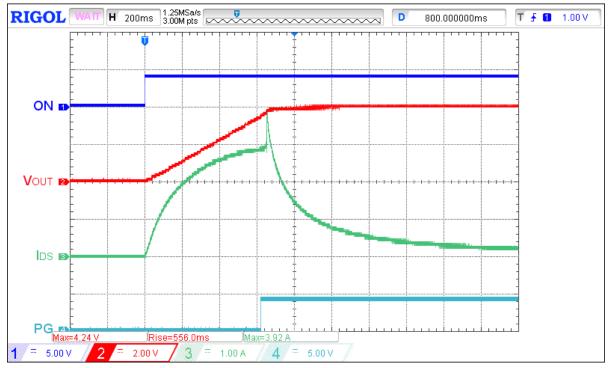

According to the above, charging supercapacitors with high currents leads to continuously switching ON/OFF IPS and a "saw" appears on the V<sub>OUT</sub> (see Figure 6). To charge up such a large load capacitor, a 2  $\mu$ F capacitor was chosen for C<sub>SLEW</sub>. It sets the slew rate to 5.75 V/s and thus limits the inrush current to 3.8 A (see Figure 7).

Even if  $C_{SLEW}$  is chosen and protection circuits are not triggered during power up, we recommend to check package-case temperature as well. If during power up, the package case temperature rises higher than 20 °C to 30 °C, we recommend increasing  $C_{SLEW}$  value until case temperature rise is less than 30°C (or lower), otherwise frequent overheating cycles may impact the IPS's long-term reliability.

| Application Note | Revision 1.0 | 03-Jul-2018 |

|------------------|--------------|-------------|

|------------------|--------------|-------------|

Figure 6: Active Current Limit and Thermal Protection Operation During Power Up on High Capacitive Load Caused by Improper IPS Slew Rate Settings for  $V_{DD} = V_{IN} = 4 \text{ V}$ ,  $I_{ACL} = 5.7 \text{ A}$ ,  $R_{SET} = 40 \text{ k}\Omega$ ,  $C_{SLEW} = 10 \text{ nF}$ ,  $C_{LOAD} = 0.66 \text{ F}$ ,  $R_{LOAD} = 100 \Omega$

© 2018 Dialog Semiconductor

### AN-CM-246

#### Using Dialog's Integrated Power Switches in Super Capacitor Applications

Figure 7: Typical Power Up for High Capacitive Load with Proper IPS Slew Rate Settings for  $V_{DD} = V_{IN} = 4 \text{ V}, I_{ACL} = 5.7 \text{ A}, R_{SET} = 40 \text{ k}\Omega, C_{SLEW} = 2 \mu\text{F}, C_{LOAD} = 0.66 \text{ F}, R_{LOAD} = 100 \Omega$

## 7 Conclusion

Charging high capacitive loads without any control may cause large inrush currents which can severely damage an IPS as well as any circuits downstream of the IPS. In addition, the charging of large capacitive loads may cause frequent over-heating cycles that can affect any IPS's long-term reliability. To solve this problem, Dialog Semiconductor offers a wide range of high-performance nFET integrated power switches with at least one or more protection features like adjustable inrush current control, active current limit, thermal shutdown protection. For more information on Dialog's family of integrated power switches with advanced features, please, visit www.dialog-semiconductor.com

© 2018 Dialog Semiconductor

## **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 03-Jul-2018 | Initial Version |

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### Disclaimer

Information in this document is believed to be accurate and reliable. However, Dialog Semiconductor does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. Dialog Semiconductor furthermore takes no responsibility whatsoever for the content in this document if provided by any information source outside of Dialog Semiconductor.

Dialog Semiconductor reserves the right to change without notice the information published in this document, including without limitation the specification and the design of the related semiconductor products, software and applications.

Applications, software, and semiconductor products described in this document are for illustrative purposes only. Dialog Semiconductor makes no representation or warranty that such applications, software and semiconductor products will be suitable for the specified use without further testing or modification. Unless otherwise agreed in writing, such testing or modification is the sole responsibility of the customer and Dialog Semiconductor excludes all liability in this respect.

Customer notes that nothing in this document may be construed as a license for customer to use the Dialog Semiconductor products, software and applications referred to in this document. Such license must be separately sought by customer with Dialog Semiconductor.

All use of Dialog Semiconductor products, software and applications referred to in this document are subject to Dialog Semiconductor's Standard Terms and Conditions of Sale, available on the company website (www.dialog-semiconductor.com) unless otherwise stated.

Dialog and the Dialog logo are trademarks of Dialog Semiconductor plc or its subsidiaries. All other product or service names are the property of their respective owners.

© 2020 Dlog Semiconductor. All rights reserved.

## **Contacting Dialog Semiconductor**

United Kingdom (Headquarters) Dialog Semiconductor (UK) LTD Phone: +44 1793 757700

#### Germany

Dialog Semiconductor GmbH Phone: +49 7021 805-0

#### The Netherlands Dialog Semiconductor B.V. Phone: +31 73 640 8822

Email: enquiry@diasemi.com

#### **Application Note**

North America

Dialog Semiconductor Inc. Phone: +1 408 845 8500

#### Japan

Dialog Semiconductor K. K. Phone: +81 3 5769 5100

#### Taiwan

Dialog Semiconductor Taiwan Phone: +886 281 786 222 Web site: www.dialog-semiconductor.com

#### Hong Kong

Dialog Semiconductor Hong Kong Phone: +852 2607 4271

#### Korea

Dialog Semiconductor Korea Phone: +82 2 3469 8200

#### China (Shenzhen)

Dialog Semiconductor China Phone: +86 755 2981 3669

China (Shanghai) Dialog Semiconductor China Phone: +86 21 5424 9058

#### **Revision 1.0**

03-Jul-2018