### **General Description**

DA9080 is a five-channel advanced, configurable, system power management IC (PMIC) with four buck regulators and one LDO. This highly integrated, flexible PMIC is capable of up to 10 A of output current. The output voltage of the regulators can be programmed and sequenced based on the application needs. The DA9080 also integrates an 8-bit ADC, along with several other features, that simplifies overall system design. Dynamic voltage control (DVC), robust protection features, and a dedicated I<sup>2</sup>C interface that supports multiple modes extend the applicability of this device to a wide range of end applications.

The high-efficiency, fast transient response, and small footprint of the DA9080 lends itself to become the preferred power solution for a host of complex, high-performance applications. The DA9080 is offered in a QFN package.

### **Key Features**

- Power supply voltage (V<sub>IN</sub>) 4.0 V to 5.5 V

- Four buck converters

- Selectable output voltage range for bucks:

- □ CH1 Buck: 2.1 V to 3.3 V, 20 mV step

- □ CH2 Buck: 1.5 V to 2.6 V, 20 mV step

- $\hfill\Box$  CH3 Buck: 0.9 V to 1.3 V, 5 mV step

- □ CH4 Buck: 0.8 V to 1.4 V, 5 mV step

- Maximum output current:

- □ CH1, CH2, and CH3 Buck: 1.5 A

- □ CH4 Buck: 5.0 A

- Interleaving of switching phases of bucks

- LDO:

- □ V<sub>OUT</sub>: 3.3 V, I<sub>OUT</sub>: 0.2 A (max)

- General purpose ADC:

- □ 8-bit SAR ADC

- □ Two external inputs

- □ Die temperature sense

- Protection functions:

- Over-current protection

- □ Over/under-voltage protection

- ☐ Thermal shutdown protection

- I<sup>2</sup>C control interface:

- □ Standard mode (100 kbit/s)

- □ Fast mode (400 kbit/s)

- □ Fast mode+ (1 Mbit/s)

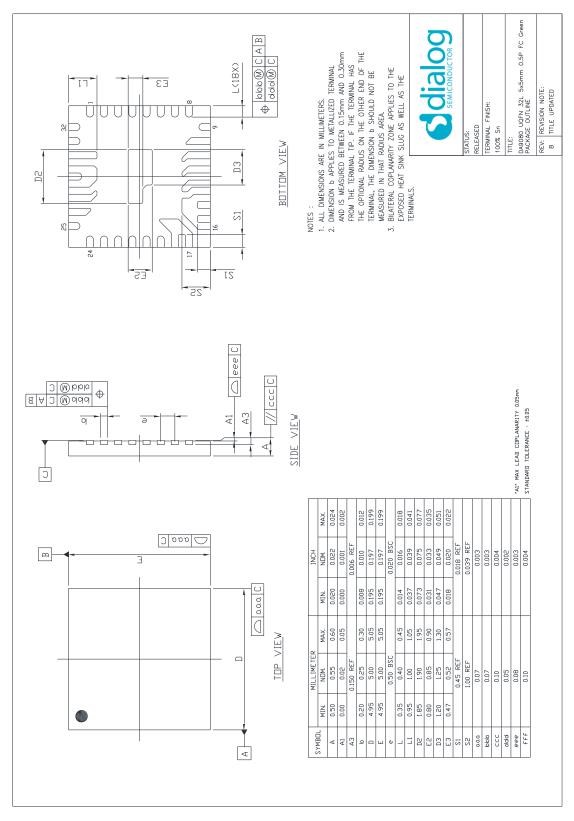

- Package: 32 lead QFN, 5.0 mm x 5.0 mm

## **Applications**

- Client and Enterprise SSD modules

- Embedded Computing

■ Integrated Microcontroller Internet of Things

© 2021 Dialog Semiconductor

DSPs or FPGAs with Peripherals

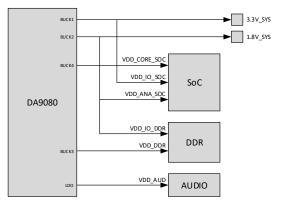

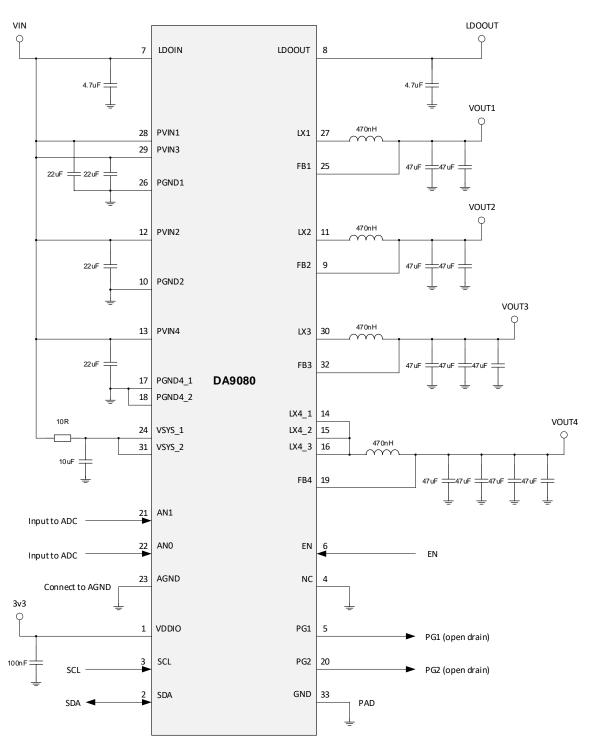

## **System Diagram**

Figure 1: System Diagram

### **Contents**

| Ge | neral   | Descrip  | tion                                                     | 1  |  |

|----|---------|----------|----------------------------------------------------------|----|--|

| Ke | y Feat  | tures    |                                                          | 1  |  |

| Аp | plicati | ions     |                                                          | 1  |  |

| Sy | stem l  | Diagran  | 1                                                        | 1  |  |

| 1  | Term    | s and D  | Definitions                                              | 5  |  |

| 2  | Refe    | rences . |                                                          | 5  |  |

| 3  |         |          | am                                                       |    |  |

| 4  |         | _        |                                                          |    |  |

| 5  |         |          | ics                                                      |    |  |

| J  | 5.1     |          | Ite Maximum Ratings                                      |    |  |

|    | 5.2     | -        |                                                          |    |  |

|    | 5.3     |          | nmended Operating Conditions                             |    |  |

|    | 5.4     |          | al Characteristics                                       |    |  |

|    | 5.5     |          | cal Characteristics                                      |    |  |

|    |         | 5.5.1    | CH1 Buck Converter Characteristics                       | 10 |  |

|    |         | 5.5.2    | CH2 Buck Converter Characteristics                       | 12 |  |

|    |         | 5.5.3    | CH3 Buck Converter Characteristics                       | 14 |  |

|    |         | 5.5.4    | CH4 Buck Converter Characteristics                       | 16 |  |

|    |         | 5.5.5    | LDO Characteristics                                      | 19 |  |

|    |         | 5.5.6    | ADC Characteristics                                      | 20 |  |

|    |         | 5.5.7    | Supervision Characteristics                              | 20 |  |

|    |         | 5.5.8    | Quiescent Current Characteristics                        | 21 |  |

|    |         | 5.5.9    | I <sup>2</sup> C Characteristics                         |    |  |

|    |         | 5.5.10   | Digital I/O Characteristics                              | 23 |  |

| 6  | Func    | tional S | States                                                   | 24 |  |

| 7  | Sequ    | encer    |                                                          | 24 |  |

|    | 7.1     | Function | onal Description                                         | 24 |  |

|    | 7.2     | Timing   | Diagrams                                                 | 26 |  |

| 8  | Supe    | rvision  |                                                          | 29 |  |

|    | 8.1     | Input V  | /oltage Monitor Flag                                     | 29 |  |

|    | 8.2     | Fault F  | Protection                                               | 29 |  |

|    |         | 8.2.1    | Over-Voltage, Under-Voltage, and Over-Current Protection | 29 |  |

|    |         | 8.2.2    | Thermal Shutdown                                         |    |  |

|    | 8.3     | Power    | Good Indicator                                           | 31 |  |

|    |         | 8.3.1    | Monitoring Groups of Power Good Indicators via PG Pins   | 31 |  |

| 9  | Buck    | Conve    | rters                                                    | 31 |  |

|    | 9.1     | Dynam    | nic Voltage Control                                      | 31 |  |

| 10 | LDO     |          |                                                          | 32 |  |

| 11 | Gene    | ral Pur  | pose Analog-to-Digital Converter                         | 32 |  |

|    | 11.1    | _        | rements on Internal Die Temperature Sensors              |    |  |

|    | 11.2    | Measu    | rements of External Analog Signals                       | 32 |  |

|    | 11.3    | Trigge   | ring GPADC Conversions                                   | 32 |  |

|    |         |          |                                                          |    |  |

**Datasheet**

07-Apr-2021

| 12  | I <sup>2</sup> C C | ommunic   | ation                              | 32              |

|-----|--------------------|-----------|------------------------------------|-----------------|

| 13  | Regis              | ter Defin | itions                             | 35              |

|     | 13.1               | Register  | Map                                | 35              |

|     | 13.2               | Register  | Descriptions                       | 37              |

|     |                    | 13.2.1    | •                                  | 37              |

|     |                    | 13.2.2    | •                                  | 46              |

| 14  | Packa              | age Infor | '                                  | 47              |

| 15  |                    | _         |                                    | 48              |

| _   |                    | •         |                                    | 49              |

|     | 16.1               |           |                                    | 50              |

|     |                    |           | •                                  | 50              |

|     |                    | ·         | · ·                                |                 |

|     | gure               |           |                                    |                 |

|     |                    |           |                                    |                 |

|     |                    |           |                                    | 6               |

|     |                    |           |                                    |                 |

|     |                    |           |                                    | or 414118       |

| Fig | ure 6:             | FSM Stat  | es                                 | 24              |

|     |                    |           |                                    | 26              |

|     |                    |           |                                    | by EN Pin       |

|     |                    |           |                                    | by DISABLE Bit  |

|     |                    |           |                                    |                 |

|     |                    |           |                                    |                 |

|     |                    |           |                                    |                 |

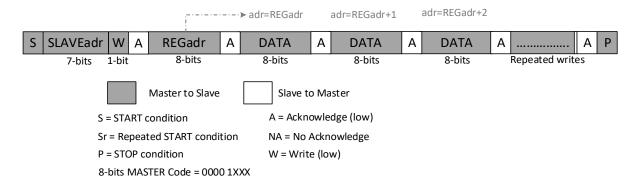

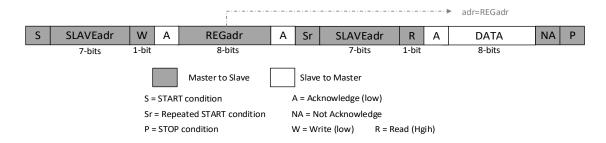

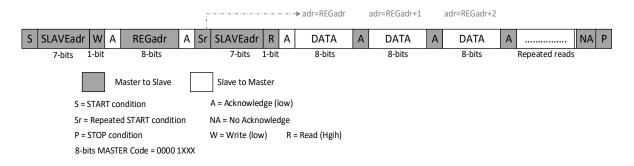

|     |                    |           |                                    | 34              |

|     |                    |           |                                    | 34              |

|     |                    |           |                                    |                 |

| Ū   | bles               |           | on Diagram                         |                 |

|     |                    |           |                                    | 7               |

|     |                    |           |                                    | 8               |

|     |                    |           |                                    | 9               |

|     |                    |           |                                    | 9               |

|     |                    |           |                                    | 10              |

| Tak | ole 7: 0           | CH1 Buck  | Converter Electrical Characteristi | cs10            |

|     |                    |           |                                    | cs12            |

|     |                    |           |                                    | cs              |

|     |                    |           |                                    | tics            |

|     |                    |           |                                    |                 |

|     |                    |           |                                    | 20              |

|     |                    |           |                                    | 21              |

|     |                    |           |                                    | 22              |

|     |                    |           |                                    | 23              |

| ıat | DIE 1/:            | Register  | мар                                | 35              |

| Dat | tashee             | et        | Revision                           | 1.1 07-Apr-2021 |

### **DA9080**

| Table 18: PMC_PGOOD_UV (0x0000)           | . 37 |

|-------------------------------------------|------|

| Table 19: PMC_CH_OC (0x0001)              |      |

| Table 20: PMC_CH_OV (0x0002)              | . 39 |

| Table 21: PMC_CH_UV (0x0003)              | . 39 |

| Table 22: PMC_ADC_ENABLE (0x0004)         | . 40 |

| Table 23: PMC_CH_EN (0x0005)              | . 40 |

| Table 24: PMC_VOUT_BUCK1 (0x0007)         | . 41 |

| Table 25: PMC_VOUT_BUCK2 (0x0008)         |      |

| Table 26: PMC_VOUT_BUCK3 (0x0009)         | . 41 |

| Table 27: PMC_VOUT_BUCK4 (0x000A)         |      |

| Table 28: PMC_PHASE_INTERLEAVING (0x000B) | . 42 |

| Table 29: PMC_BUCK_SEQ_GRP (0x000C)       | . 42 |

| Table 30: PMC_LDO_SEQ_GRP (0x000D)        | . 43 |

| Table 31: PMC_PG1 (0x000E)                | . 43 |

| Table 32: PMC_PG2 (0x000F)                |      |

| Table 33: PMC_DISCHARGE (0x0010)          |      |

| Table 34: PMC_TEMP (0x0011)               |      |

| Table 35: PMC_ADC0 (0x0012)               |      |

| Table 36: PMC_ADC1 (0x0013)               |      |

| Table 37: PMC_REVISION_ID (0x0014)        |      |

| Table 38: OTP_CONFIG_ID (0x0062)          |      |

| Table 39: Ordering Information            | . 48 |

| Table 40: Recommended External Components | . 50 |

| Table 41: Capacitor Derating Values       | . 50 |

#### 1 Terms and Definitions

ADC Analog to digital converter

CH<x> Channel <x>, where x = 1 to 4

DVC Dynamic voltage control

**ESD** Electrostatic discharge **GPADC** General purpose ADC LDO Low dropout regulator MSB Most significant bit OCP Over-current protection OTP One-time programmable OVP Over-voltage protection OVLO Over-voltage lockout

PFM Pulse frequency modulation

PMIC Power management integrated circuit

POR Power-on reset

PWM Pulse width modulation

SAR Successive approximation register

TSD Thermal shutdown

UQFN Ultra-thin quad flat-pack no-lead (package)

UVP Under-voltage protection UVLO Under-voltage lockout

#### 2 References

[1] NXP Semiconductors N.V., UM10204 I<sup>2</sup>C-Bus Specification and User Manual, Revision 6

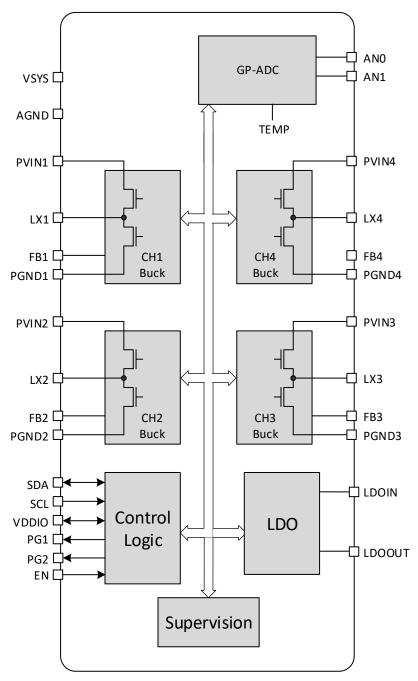

### 3 Block Diagram

Figure 2: Block Diagram

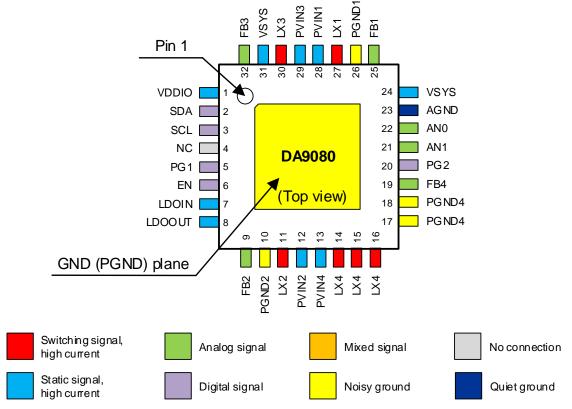

#### 4 Pinout

Figure 3: UQFN Pinout Diagram (Top View)

**Table 1: Pin Description**

| Pin#       | Pin<br>Name | Type<br>(Table 2) | Description                                                                                |

|------------|-------------|-------------------|--------------------------------------------------------------------------------------------|

| 1          | VDDIO       | PWR               | Supply for I <sup>2</sup> C interface                                                      |

| 2          | SDA         | DIOD              | I <sup>2</sup> C interface data, connect SDA to the logic rail via a pull-up resistor      |

| 3          | SCL         | DI                | I <sup>2</sup> C interface data, connect SCL to the logic rail via a pull-up resistor      |

| 4          | NC          | DI                | Not used, connect to GND                                                                   |

| 5          | PG1         | DO                | Power good output 1, open drain                                                            |

| 6          | EN          | DI                | Chip enable (when pulled low, shuts down entire chip after power down sequencing complete) |

| 7          | LDOIN       | PWR               | LDO input, bypass to ground with a ceramic capacitor                                       |

| 8          | LDOOUT      | PWR               | Output of LDO                                                                              |

| 9          | FB2         | AI                | CH2 Buck output voltage feedback connection                                                |

| 10         | PGND2       | GND               | CH2 Buck converter power ground                                                            |

| 11         | LX2         | PWR               | CH2 Buck converter switching node                                                          |

| 12         | PVIN2       | PWR               | CH2 Buck converter input                                                                   |

| 13         | PVIN4       | PWR               | CH4 Buck converter input                                                                   |

| 14, 15, 16 | LX4         | PWR               | CH4 Buck converter switching node                                                          |

| 17, 18     | PGND4       | GND               | CH4 Buck converter power ground                                                            |

| Pin#   | Pin<br>Name | Type (Table 2) | Description                                                   |

|--------|-------------|----------------|---------------------------------------------------------------|

| 19     | FB4         | Al             | CH4 Buck output voltage feedback connection                   |

| 20     | PG2         | DO             | Power good output 1, open drain                               |

| 21     | AN1         | Al             | Input to ADC                                                  |

| 22     | AN0         | Al             | Input to ADC                                                  |

| 23     | AGND        | GND            | Quiet ground connection, connect to a quiet ground area       |

| 24, 31 | VSYS        | PWR            | Filtered from VIN through an RC to provide a clean 5 V supply |

| 25     | FB1         | Al             | CH1 Buck output voltage feedback connection                   |

| 26     | PGND1       | GND            | CH1 Buck converter power ground                               |

| 27     | LX1         | PWR            | CH1 Buck converter switching node                             |

| 28     | PVIN1       | PWR            | CH1 Buck converter input – internally connected to PVIN3      |

| 29     | PVIN3       | PWR            | CH3 Buck converter input – internally connected to PVIN1      |

| 30     | LX3         | PWR            | CH3 Buck converter switching node                             |

| 32     | FB3         | Al             | CH3 Buck output voltage feedback connection                   |

| PAD    | GND         | GND            | Package central pad, connect to PGND                          |

### **Table 2: Pin Type Definition**

| Pin Type | Description                     | Pin Type | Description         |

|----------|---------------------------------|----------|---------------------|

| DI       | Digital input                   | Al       | Analog input        |

| DO       | Digital output                  | AIO      | Analog input/output |

| DIO      | Digital input/output            | PWR      | Power               |

| DIOD     | Digital input/output open drain | GND      | Ground              |

#### 5 Characteristics

#### 5.1 Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

**Table 3: Absolute Maximum Ratings**

| Parameter        | Description           | Conditions         | Min  | Тур | Max | Unit |

|------------------|-----------------------|--------------------|------|-----|-----|------|

| T <sub>STG</sub> | Storage temperature   |                    | -60  |     | 150 | °C   |

| V <sub>SYS</sub> | System supply voltage | Referenced to AGND | -0.3 |     | 6   | V    |

| V <sub>PIN</sub> | All other pins        | Referenced to AGND | -0.3 |     | 6   | V    |

#### **5.2 Electrostatic Discharge Ratings**

**Table 4: Electrostatic Discharge Ratings**

| Parameter            | Description            | Conditions                                 | Value | Unit |

|----------------------|------------------------|--------------------------------------------|-------|------|

| Vesd_HBM             | Maximum ESD protection | Human body model (HBM)<br>All exposed pins | 2     | kV   |

| V <sub>ESD_CDM</sub> | Maximum ESD protection | Charged device model (CDM)                 | 0.5   | kV   |

#### **5.3** Recommended Operating Conditions

**Table 5: Recommended Operating Conditions**

| Parameter        | Description                    | Conditions | Min  | Тур | Max         | Unit |

|------------------|--------------------------------|------------|------|-----|-------------|------|

| T <sub>A</sub>   | Operating ambient temperature  |            | -40  |     | 85          | °C   |

| TJ               | Operating junction temperature |            | -40  |     | 125         | °C   |

| Vsys             | Input supply voltage           |            | 4    |     | 5.5         | V    |

| V <sub>PIN</sub> | Voltage on all other pins      |            | -0.3 |     | VIN+0.<br>3 | V    |

#### 5.4 Thermal Characteristics

**Table 6: UQFN Ratings**

| Parameter         | Description                         | Conditions                                                          | Min | Тур | Max  | Unit |

|-------------------|-------------------------------------|---------------------------------------------------------------------|-----|-----|------|------|

| R <sub>O_JA</sub> | Package thermal resistance (Note 1) |                                                                     |     |     | 24.3 | °C/W |

| P <sub>D</sub>    | Power dissipation                   | Derating factor above $T_A = 65$ °C, 41.1 mW/°C $(1/R_{\Theta_J}A)$ |     |     | 2.47 | W    |

**Note 1** Obtained from package thermal simulation, JEDEC JESD51-2 still air test environment using 4-layer board at T<sub>A</sub> = 65 °C with 36 vias. Influenced by PCB technology and layout.

#### 5.5 Electrical Characteristics

All Min/Max specification limits are guaranteed by design, production testing, and/or statistical characterization and are valid over the full operating temperature range and power supply range unless otherwise noted.

Typical values are based on characterization results at default measurement conditions and are informative only. Default measurement conditions (unless otherwise specified):  $V_{IN} = 5.0 \text{ V}$ ,  $T_A = 25 \,^{\circ}\text{C}$ .

#### 5.5.1 CH1 Buck Converter Characteristics

**Table 7: CH1 Buck Converter Electrical Characteristics**

| Parameter       | Description                                                       | Conditions                       | Min  | Тур  | Max  | Unit |

|-----------------|-------------------------------------------------------------------|----------------------------------|------|------|------|------|

| External Ele    | ectrical Conditions                                               |                                  |      |      |      |      |

| V <sub>IN</sub> | Input voltage of power stage                                      |                                  | 4    | 5    | 5.5  | V    |

| Соит            | Output capacitance, including voltage and temperature coefficient | 2 x 47 µF                        | 21   |      | 68   | μF   |

| ESRCOUT         | Output capacitor series resistance                                | f > 100 kHz                      |      | 3    |      | mΩ   |

| L               | Inductor value, including current and temperature dependence      |                                  | 0.23 | 0.47 | 0.61 | μH   |

| DCRL            | Inductor DC resistance                                            |                                  |      | 20   | 50   | mΩ   |

| Electrical Po   | erformance                                                        |                                  |      |      |      |      |

| Гоит            | Maximum output current                                            |                                  | 1500 |      |      | mA   |

| IQ_AUTO         | Quiescent current in Auto mode (no switching)                     |                                  |      | 51   |      | μΑ   |

| f <sub>SW</sub> | Switching frequency                                               |                                  | 1.9  | 2    | 2.1  | MHz  |

| Vouт            | Range of output voltage, programmable in 20 mV steps              | V <sub>IN</sub> = 4.0 V to 5.5 V | 2.1  | 3.3  | 3.3  | V    |

| Parameter           | Description                                                          | Conditions                                                                                                                                                                                                                                                                                                                                                          | Min   | Тур  | Max  | Unit  |

|---------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| Vout_stp            | Output voltage programable step                                      |                                                                                                                                                                                                                                                                                                                                                                     |       | 20   |      | mV    |

| Vout_ACC_DF         | Accuracy of default output voltage                                   | In PWM mode Vout = 3.3 V Iout = 1 A                                                                                                                                                                                                                                                                                                                                 | 3.267 | 3.3  | 3.33 | V     |

| Vout_acc_lin        | Static line regulation                                               |                                                                                                                                                                                                                                                                                                                                                                     |       | 0.5  |      | %/V   |

| Vout_acc_ld         | Static load regulation                                               | In PWM mode<br>Iout = 1.5 A                                                                                                                                                                                                                                                                                                                                         |       | 0.1  |      | %/A   |

| Vout_acc_ac         | Output voltage accuracy, including PWM/PFM ripple and load transient | Vout = $3.3 \text{ V}$<br>Cout = $2 \text{ x } 47 \text{ \muF}$<br>Load transient 1: from $0.5^*\text{I}_{\text{MAX}}$ to $1_{\text{MAX}}$ in $0.2 \text{ A/}_{\text{\muS}}$<br>Load transient 2: from 50 mA to $0.5^*\text{I}_{\text{MAX}}$ in $0.2 \text{ A/}_{\text{\muS}}$<br>$1_{\text{MAX}} = 1.5 \text{ A}$<br>Vin = $5.0 \text{ V}$<br>Ta = $25 \text{ °C}$ | -2    |      | 3    | %     |

| IPOSLIM             | Positive over-current limit threshold                                |                                                                                                                                                                                                                                                                                                                                                                     | 3     | 4    |      | А     |

| VTHR_OVP_RIS        | Over-voltage protection threshold                                    |                                                                                                                                                                                                                                                                                                                                                                     | 200   | 300  | 400  | mV    |

| VTHR_UVP_FA         | Under-voltage protection threshold                                   |                                                                                                                                                                                                                                                                                                                                                                     | -400  | -300 | -200 | mV    |

| RDCHG               | Discharge resistance for LX node                                     |                                                                                                                                                                                                                                                                                                                                                                     |       | 67   |      | Ω     |

| ton_min             | Buck LX minimum on time                                              |                                                                                                                                                                                                                                                                                                                                                                     |       | 20   |      | ns    |

| SR <sub>SS</sub>    | Soft start slew rate                                                 |                                                                                                                                                                                                                                                                                                                                                                     |       | 2.5  |      | mV/μs |

| SR <sub>SDCHG</sub> | Soft discharge slew rate                                             |                                                                                                                                                                                                                                                                                                                                                                     |       | 2.5  |      | mV/μs |

#### 5.5.2 CH2 Buck Converter Characteristics

#### **Table 8: CH2 Buck Converter Electrical Characteristics**

| Parameter           | Description                                                                    | Conditions                              | Min   | Тур  | Max   | Unit |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------------|-------|------|-------|------|

| External Ele        | ectrical Conditions                                                            |                                         |       |      |       |      |

| VIN                 | Input voltage of power stage                                                   |                                         | 4     | 5    | 5.5   | V    |

| Соит                | Output capacitance, including voltage and temperature coefficient              | 2 x 47 µF                               | 30    |      | 85    | μF   |

| ESRCOUT             | Output capacitor series resistance                                             | f > 100 kHz                             |       | 3    |       | mΩ   |

| L                   | Inductor value, including current and temperature dependence                   |                                         | 0.23  | 0.47 | 0.61  | μH   |

| DCRL                | Inductor DC resistance                                                         |                                         |       | 20   | 50    | mΩ   |

| Electrical Po       | erformance                                                                     |                                         |       |      |       |      |

| louт                | Maximum output current                                                         |                                         | 1500  |      |       | mA   |

| I <sub>Q_AUTO</sub> | Quiescent current in Auto mode (no switching)                                  |                                         |       | 51   |       | μΑ   |

| fsw                 | Switching frequency                                                            |                                         | 1.9   | 2    | 2.1   | MHz  |

| Vouт                | Output voltage range,<br>programmable in 20 mV<br>steps                        | V <sub>IN</sub> = 4.0 V to 5.5 V        | 1.5   | 1.8  | 2.6   | V    |

| Vout_stp            | Output voltage programable step                                                |                                         |       | 20   |       | mV   |

| Vout_acc_df         | Accuracy of default output voltage                                             | In PWM mode Vout = 1.8 V Iout = 1 A     | 1.782 | 1.8  | 1.818 | V    |

| Vout_acc_dc         | Output voltage accuracy in PWM mode, including static line and load regulation |                                         | -1    |      | 1     | %    |

| Vout_acc_lin        | Static line regulation                                                         |                                         |       | 0.5  |       | %/V  |

| Vout_acc_ld         | Static load regulation                                                         | In PWM mode<br>I <sub>OUT</sub> = 1.5 A |       | 0.1  |       | %/A  |

| Parameter           | Description                                                          | Conditions                                                                                                                                                                                                                                 | Min  | Тур  | Max  | Unit  |

|---------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Vout_acc_ac         | Output voltage accuracy, including PWM/PFM ripple and load transient | $V_{OUT}$ = 1.8 V<br>$C_{OUT}$ = 2 x 47 μF<br>Load transient 1: from<br>$0.5*I_{MAX}$ to $I_{MAX}$ in 0.2 A/μs<br>Load transient 2: from 50 mA<br>to $0.5*I_{MAX}$ in 0.2 A/μs<br>$I_{MAX}$ = 1.5 A<br>$V_{IN}$ = 5.0 V<br>$T_{A}$ = 25 °C | -2   |      | 3    | %     |

| IPOSLIM             | Positive over-current limit threshold                                |                                                                                                                                                                                                                                            | 3    | 4    |      | А     |

| VTHR_OVP_RIS        | Over-voltage protection threshold                                    |                                                                                                                                                                                                                                            | 200  | 300  | 400  | mV    |

| VTHR_UVP_FA         | Under-voltage protection threshold                                   |                                                                                                                                                                                                                                            | -400 | -300 | -200 | mV    |

| RDCHG               | Discharge resistance for LX node                                     |                                                                                                                                                                                                                                            |      | 67   |      | Ω     |

| ton_min             | Buck LX minimum on time                                              |                                                                                                                                                                                                                                            |      | 20   |      | ns    |

| SR <sub>SS</sub>    | Soft start slew rate                                                 |                                                                                                                                                                                                                                            |      | 2.5  |      | mV/μs |

| SR <sub>SDCHG</sub> | Soft discharge slew rate                                             |                                                                                                                                                                                                                                            |      | 2.5  |      | mV/μs |

#### 5.5.3 CH3 Buck Converter Characteristics

**Table 9: CH3 Buck Converter Electrical Characteristics**

| Parameter           | Description                                                          | Conditions                                                                                                                                                                                                                                                                            | Min   | Тур  | Max    | Unit |

|---------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------|------|

| External Ele        | ctrical Conditions                                                   |                                                                                                                                                                                                                                                                                       |       |      |        |      |

| VIN                 | Input voltage of power stage                                         |                                                                                                                                                                                                                                                                                       | 4     | 5    | 5.5    | V    |

| Соит                | Output capacitance, including voltage and temperature coefficient    | 3 x 47 µF                                                                                                                                                                                                                                                                             | 70    |      | 153    | μF   |

| ESR <sub>COUT</sub> | Output capacitor series resistance                                   | f > 100 kHz                                                                                                                                                                                                                                                                           |       | 3    |        | mΩ   |

| L                   | Inductor value, including current and temperature dependence         |                                                                                                                                                                                                                                                                                       | 0.23  | 0.47 | 0.61   | μH   |

| DCRL                | Inductor DC resistance                                               |                                                                                                                                                                                                                                                                                       |       | 20   | 50     | mΩ   |

| Electrical Pe       | erformance                                                           |                                                                                                                                                                                                                                                                                       |       |      |        |      |

| lоит                | Maximum output current                                               |                                                                                                                                                                                                                                                                                       | 1500  |      |        | mA   |

| IQ_AUTO             | Quiescent current in Auto mode (no switching)                        |                                                                                                                                                                                                                                                                                       |       | 56   |        | μΑ   |

| fsw                 | Switching frequency                                                  |                                                                                                                                                                                                                                                                                       | 1.9   | 2    | 2.1    | MHz  |

| V <sub>OUT</sub>    | Output voltage range                                                 | V <sub>IN</sub> = 4.0 V to 5.5 V                                                                                                                                                                                                                                                      | 0.9   | 1.2  | 1.3    | V    |

| Vout_stp            | Output voltage programable step                                      |                                                                                                                                                                                                                                                                                       |       | 5    |        | mV   |

| Vout_acc_df<br>lt   | Accuracy of default output voltage                                   | In PWM mode Vout = 1.2 V Iout = 1 A                                                                                                                                                                                                                                                   | 1.188 | 1.2  | 1.1212 | V    |

| Vout_acc_lin        | Static line regulation                                               |                                                                                                                                                                                                                                                                                       |       | 0.5  |        | %/V  |

| Vout_acc_ld         | Static load regulation                                               | In PWM mode                                                                                                                                                                                                                                                                           |       | 0.1  |        | %/A  |

| Vout_acc_ac         | Output voltage accuracy, including PWM/PFM ripple and load transient | $V_{OUT} = 1.2 \text{ V}$ $C_{OUT} = 3 \text{ x } 47 \text{ μF}$ Load transient 1: from 0.5*I <sub>MAX</sub> to I <sub>MAX</sub> in 0.2 A/μs Load transient 2: from 50 mA to 0.5*I <sub>MAX</sub> in 0.2 A/μs I <sub>MAX</sub> = 1.5 A $V_{IN} = 5.0 \text{ V}$ $T_A = 25 \text{ °C}$ | -2    |      | 4      | %    |

| IPOSLIM             | Positive over-current limit threshold                                |                                                                                                                                                                                                                                                                                       | 3     | 4    |        | Α    |

## **DA9080**

| Parameter           | Description                        | Conditions | Min  | Тур  | Max  | Unit  |

|---------------------|------------------------------------|------------|------|------|------|-------|

| VTHR_OVP_RIS        | Over-voltage protection threshold  |            | 200  | 300  | 400  | mV    |

| VTHR_UVP_FA         | Under-voltage protection threshold |            | -400 | -300 | -200 | mV    |

| SR <sub>DVC</sub>   | Output voltage slew rate           |            |      | 10   |      | mV/μs |

| RDCHG               | Discharge resistance for LX node   |            |      | 67   |      | Ω     |

| ton_min             | Buck LX minimum on time            |            |      | 20   |      | ns    |

| SR <sub>SS</sub>    | Soft start slew rate               |            |      | 1.25 |      | mV/μs |

| SR <sub>SDCHG</sub> | Soft discharge slew rate           |            |      | 1.25 |      | mV/μs |

#### 5.5.4 CH4 Buck Converter Characteristics

**Table 10: CH4 Buck Converter Electrical Characteristics**

| Parameter        | Description                                                          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                      | Min  | Тур  | Max  | Unit |  |  |  |

|------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|

| External Ele     | External Electrical Conditions                                       |                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |  |  |  |

| VIN              | Input voltage of power stage                                         |                                                                                                                                                                                                                                                                                                                                                                                                                 | 4    | 5    | 5.5  | V    |  |  |  |

| Соит             | Output capacitance, including voltage and temperature coefficient    | 4 x 47 μF                                                                                                                                                                                                                                                                                                                                                                                                       | 94   |      | 203  | μF   |  |  |  |

| ESRcout          | Output capacitor series resistance                                   | f > 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                     |      | 3    |      | mΩ   |  |  |  |

| L                | Inductor value, including current and temperature dependence         |                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.23 | 0.47 | 0.61 | μН   |  |  |  |

| DCRL             | Inductor DC resistance                                               |                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 20   | 50   | mΩ   |  |  |  |

| Electrical Pe    | erformance                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |  |  |  |

| Гоит             | Maximum output current                                               |                                                                                                                                                                                                                                                                                                                                                                                                                 | 5000 |      |      | mA   |  |  |  |

| IQ_AUTO          | Quiescent current in Auto mode (no switching)                        |                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 56   |      | μΑ   |  |  |  |

| fsw              | Switching frequency                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.9  | 2    | 2.1  | MHz  |  |  |  |

| V <sub>OUT</sub> | Output voltage range                                                 | V <sub>IN</sub> = 4.0 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                                | 0.8  | 1    | 1.4  | V    |  |  |  |

| Vout_stp         | Output voltage programable step                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 5    |      | mV   |  |  |  |

| Vout_acc_df      | Accuracy of default output voltage                                   | In PWM mode Vout = 1.0 V Iout = 1 A                                                                                                                                                                                                                                                                                                                                                                             | 0.99 | 1    | 1.01 | V    |  |  |  |

| Vout_acc_lin     | Static line regulation                                               |                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 0.5  |      | %/V  |  |  |  |

| Vout_acc_ld      | Static load regulation                                               | In PWM mode                                                                                                                                                                                                                                                                                                                                                                                                     |      | 0.1  |      | %/A  |  |  |  |

| Vout_acc_ac      | Output voltage accuracy, including PWM/PFM ripple and load transient | $V_{OUT} = 1.0 \text{ V}$ $C_{OUT} = 4 \text{ x } 47 \mu\text{F}$ $Load \text{ transient } 1\text{: from }$ $0.5^*\text{I}_{MAX} \text{ to } \text{I}_{MAX} \text{ in } 0.2 \text{ A}/\mu\text{s}$ $Load \text{ transient } 2\text{: from } 50 \text{ mA}$ $\text{to } 0.5^*\text{I}_{MAX} \text{ in } 0.2 \text{ A}/\mu\text{s}$ $\text{I}_{MAX} = 5 \text{ A}$ $V_{IN} = 5.0 \text{ V}$ $T_A = 25 \text{ °C}$ | -4   |      | 4    | %    |  |  |  |

| Parameter              | Description                                                                       | Conditions                                                                                                                                                     | Min  | Тур  | Max  | Unit  |

|------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Vout_acc_ac<br>dc_full | Output voltage accuracy, including PWM/PFM ripple and load transient in full load | $V_{OUT}$ = 1.0 V<br>$C_{OUT}$ = 4 x 47 μF<br>Load transient: from 50 mA<br>to $I_{MAX}$ in 0.2 A/μs<br>$I_{MAX}$ = 5 A<br>$V_{IN}$ = 5.0 V<br>$T_{A}$ = 25 °C | -5   |      | 5    | %     |

| IPOSLIM                | Positive over-current limit threshold                                             |                                                                                                                                                                | 7    | 8.5  |      | А     |

| VTHR_OVP_RIS           | Over-voltage protection threshold                                                 |                                                                                                                                                                | 200  | 300  | 400  | mV    |

| VTHR_UVP_FA            | Under-voltage protection threshold                                                |                                                                                                                                                                | -400 | -300 | -200 | mV    |

| SR <sub>DVC</sub>      | Output voltage slew rate                                                          |                                                                                                                                                                |      | 10   |      | mV/μs |

| RDCHG                  | Discharge resistance for LX node                                                  |                                                                                                                                                                |      | 67   |      | Ω     |

| ton_min                | Buck LX minimum on time                                                           |                                                                                                                                                                |      | 20   |      | ns    |

| SRss                   | Soft start slew rate                                                              |                                                                                                                                                                |      | 1.25 |      | mV/μs |

| SR <sub>SDCHG</sub>    | Soft discharge slew rate                                                          |                                                                                                                                                                |      | 1.25 |      | mV/μs |

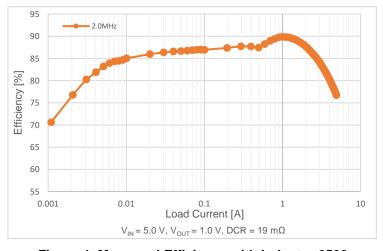

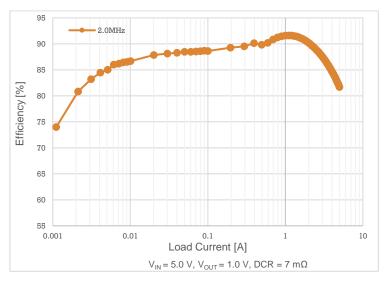

#### 5.5.4.1 CH4 Buck Converter Efficiency Characteristics

Figure 4: Measured Efficiency with Inductor 2520

Figure 5: Measured Efficiency with Low DCR Inductor 4141

#### 5.5.5 LDO Characteristics

**Table 11: LDO Electrical Characteristics**

| Parameter                | Description                                                       | Conditions                                                                                                                               | Min   | Тур  | Max  | Unit |

|--------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| External Ele             | ctrical Conditions                                                |                                                                                                                                          |       |      |      |      |

| VIN                      | Input voltage of power stage                                      |                                                                                                                                          | 4     | 5    | 5.5  | V    |

| Соит                     | Output capacitance, including voltage and temperature coefficient |                                                                                                                                          | 2.3   | 4.7  | 6.1  | μF   |

| Electrical Pe            | erformance                                                        |                                                                                                                                          |       |      |      |      |

| Гоит                     | Maximum output current                                            |                                                                                                                                          | 200   |      |      | mA   |

| Iq                       | Quiescent current                                                 |                                                                                                                                          |       | 3.7  |      | μA   |

| Vout                     | Output voltage                                                    |                                                                                                                                          |       | 3.3  |      | V    |

| Vout_ACC_DF              | Accuracy of default output voltage                                | $V_{IN} = 5 \text{ V}$ $I_{OUT} = 10 \text{ mA}$ $T_A = 25 \text{ °C}$                                                                   | 3.267 | 3.3  | 3.33 | V    |

| Vout_acc_lin             | Static line regulation                                            | Iоит = 10 mA                                                                                                                             |       | 0.1  |      | %/V  |

| Vout_acc_ld              | Static load regulation                                            | I <sub>OUT</sub> = 0 mA to 0.2 A                                                                                                         |       | 0.83 |      | %/A  |

| Vout_acc_ac              | Output voltage accuracy including load transient                  | $C_{OUT}$ = 4.7 $\mu$ F<br>Transient1: Load = 5 mA to<br>50 mA @ 0.2 A/ $\mu$ s<br>Transient2: Load = 50 mA to<br>0.1 A @ 0.2 A/ $\mu$ s | -30   |      | 30   | mV   |

| t <sub>SS</sub>          | Soft start time (not DVC controlled)                              | No load condition<br>C <sub>OUT</sub> = 4.7 μF                                                                                           |       | 0.56 | 0.8  | ms   |

| tss_тоит                 | Soft start timeout time                                           |                                                                                                                                          |       | 1.3  |      | ms   |

| tldo_off                 | Time slot allocated for LDO off sequence                          |                                                                                                                                          |       | 1.3  |      | ms   |

| I <sub>INRUSH</sub>      | Inrush current                                                    | V <sub>IN</sub> = 5 V<br>T <sub>A</sub> = 25 °C<br>C <sub>OUT</sub> = 4.7 μF                                                             |       |      | 300  | mA   |

| I <sub>LIM</sub>         | Current limit threshold                                           | C <sub>OUT</sub> = 4.7 μF                                                                                                                | 200   |      |      | mA   |

| VTHR_UVP_FA              | Under-voltage protection threshold                                |                                                                                                                                          |       | 2.92 |      | V    |

| V <sub>THR_PG_RISE</sub> | Power-good threshold                                              |                                                                                                                                          |       | 3    |      | V    |

| V <sub>HYS_PG</sub>      | Power-good hysteresis                                             |                                                                                                                                          |       | 80   |      | mV   |

| Vdropout                 | Voltage drop from LDOIN to LDOOUT                                 | I <sub>OUT</sub> = 200 mA<br>T <sub>A</sub> = 25 °C<br>C <sub>OUT</sub> = 4.7 μF                                                         |       | 200  | 400  | mV   |

Datasheet Revision 1.1 07-Apr-2021

| Parameter | Description          | Conditions | Min | Тур | Max | Unit |

|-----------|----------------------|------------|-----|-----|-----|------|

| RDCHG     | Discharge resistance |            |     | 47  |     | Ω    |

#### 5.5.6 ADC Characteristics

#### **Table 12: ADC Electrical Characteristics**

| Parameter              | Description                   | Conditions                                        | Min | Тур   | Max | Unit        |  |  |

|------------------------|-------------------------------|---------------------------------------------------|-----|-------|-----|-------------|--|--|

| Electrical Performance |                               |                                                   |     |       |     |             |  |  |

| V <sub>IN</sub>        | AN0/1 Input voltage range     |                                                   | 0   |       | 5.1 | V           |  |  |

| R <sub>IN</sub>        | AN0/1 Input Resistance        |                                                   |     | 1.235 |     | ΜΩ          |  |  |

| М                      | ADC resolution                |                                                   |     | 8     |     | bit         |  |  |

| Verr_rt                | Total conversion error        | AN0/1 = 0.05 V to 5.1 V<br>T <sub>A</sub> = 25 °C | -20 |       | 20  | mV          |  |  |

| V <sub>ERR</sub>       | Total conversion error        | AN0/1 = 0.05 V to 5.1 V                           | -40 |       | 40  | mV          |  |  |

| Vors                   | 0 V input offset error        | AN0/1 = 0 V                                       | -40 |       | 50  | mV          |  |  |

| DNL                    | Differential non-linearity    | AN0/1 = 0.05 V to 5.1 V                           | -1  |       | 1   | LSB         |  |  |

| INL                    | Integral non-linearity        | AN0/1 = 0.05 V to 5.1 V                           | -2  |       | 2   | LSB         |  |  |

| V <sub>RES</sub>       | Voltage resolution            | With respect to AN0/1                             |     | 20    |     | mV/LS<br>B  |  |  |

| T <sub>RES_SENSE</sub> | Temperature sensor resolution | Per step                                          |     | -1.97 |     | °C/ste<br>p |  |  |

| tacq_tot               | Total acquisition Time        |                                                   |     | 100   |     | μs          |  |  |

| lq                     | Quiescent current             | ADC enabled                                       |     | 160   |     | μA          |  |  |

#### **5.5.7** Supervision Characteristics

**Table 13: Supervision Electrical Characteristics**

| Parameter              | Description                                                | Conditions     | Min | Тур | Max | Unit |  |  |

|------------------------|------------------------------------------------------------|----------------|-----|-----|-----|------|--|--|

| Electrical Performance |                                                            |                |     |     |     |      |  |  |

| tFALL_DEB              | VSYS UVLO/VINGOOD Falling Debounce time                    |                |     | 10  |     | μs   |  |  |

| trise_deb              | VSYS UVLO/VINGOOD<br>Rising Debounce time                  |                |     | 1   |     | ms   |  |  |

| VTHR_UVLO_F            | V <sub>IN</sub> UVLO threshold for V <sub>IN</sub> falling |                |     | 3.6 |     | ٧    |  |  |

| VTHR_UVLO_H<br>YS      | V <sub>IN</sub> UVLO hysteresis                            |                |     | 0.2 |     | V    |  |  |

| V <sub>THR_RISE</sub>  | Input voltage good threshold                               | Voltage rising |     | 4.6 |     | V    |  |  |

Datasheet Revision 1.1 07-Apr-2021

| Parameter             | Description                           | Conditions  | Min | Тур | Max | Unit |

|-----------------------|---------------------------------------|-------------|-----|-----|-----|------|

| VTHR_RISE_AC          | Input voltage good threshold accuracy |             | -2  |     | 2   | %    |

| V <sub>THR_HYS</sub>  | Input voltage good hysteresis         |             |     | 0.2 |     | V    |

| T <sub>THR_SHDN</sub> | Thermal shutdown threshold            |             | 130 | 140 | 150 | °C   |

| TTHR_SHDN_H YS        | Thermal shutdown hysteresis           |             |     | 15  |     | °C   |

| t <sub>FLT_DEB</sub>  | Fault detect debounce time            | OVP and UVP |     | 10  |     | μs   |

| tHICCUP               | Hiccup restart delay                  |             |     | 64  |     | ms   |

| tpg                   | Individual supply PG delay            |             |     | 2   |     | ms   |

| tPG1_2                | PG1 and PG2 pins PG delay             |             |     | 10  |     | ms   |

### 5.5.8 Quiescent Current Characteristics

**Table 14: Quiescent Current Characteristics**

| Parameter              | Description                                                  | Conditions                                                                                                       | Min | Тур | Max | Unit |  |  |

|------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Electrical Performance |                                                              |                                                                                                                  |     |     |     |      |  |  |

| Ivsys_shdn             | Total current of VSYS pin                                    | SHUTDOWN mode  Vsys = 5 V  VDDIO = 0 V  TA = -40 °C to 85 °C  EN = L or  FORCE_DISABLE = H  CH <x> = All OFF</x> |     | 10  | 30  | μА   |  |  |

| IPVINX_SHDN            | Total current from PVIN1,<br>PVIN2, PVIN3, and PVIN4<br>pins | SHUTDOWN mode  Vsys = 5 V  VDDIO = 0 V  TA = -40 °C to 85 °C  EN = L or  FORCE_DISABLE = H  CH <x> = All OFF</x> |     | 0   | 10  | μА   |  |  |

| ILDOIN_SHDN            | Total current of LDOIN pin                                   | SHUTDOWN mode  Vsys = 5 V  VDDIO = 0 V  TA = -40 °C to 85 °C  EN = L or  FORCE_DISABLE = H  CH <x> = All OFF</x> |     | 0   | 1   | μА   |  |  |

| Parameter | Description                                                  | Conditions                                                                                                                                                               | Min | Тур  | Max | Unit |

|-----------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Ivsys_op  | Total current of VSYS pin                                    | OPERATING mode EN = H and FORCE_DISABLE = L CH <x> = All ON Buck: ON with no switching and no load LDO: ON with no load ADC: ON IO: Non I<sup>2</sup>C communication</x> |     | 500  | 600 | μΑ   |

| IPVINX_OP | Total current from PVIN1,<br>PVIN2, PVIN3, and PVIN4<br>pins | OPERATING mode EN = H and FORCE_DISABLE = L CH <x> = All ON Buck: ON with no switching and no load</x>                                                                   |     | 0    | 10  | μΑ   |

| Ivddio    | Total current from VDDIO pin                                 | No I <sup>2</sup> C communication<br>V <sub>SYS</sub> = 5 V<br>V <sub>DDIO</sub> = 3.3 V<br>SCL = SDA = H                                                                |     | 0.16 | 1   | μА   |

| ILDOIN_OP | Total current of LDOIN pin                                   | OPERATING mode EN = H and FORCE_DISABLE = L CH <x> = All ON LDO: ON with no load</x>                                                                                     |     | 2.7  | 10  | μА   |

#### 5.5.9 I<sup>2</sup>C Characteristics

#### **Table 15: I2C Electrical Characteristics**

| Parameter              | Description                                      | Conditions | Min  | Тур | Max  | Unit |  |  |  |

|------------------------|--------------------------------------------------|------------|------|-----|------|------|--|--|--|

| Electrical Performance |                                                  |            |      |     |      |      |  |  |  |

| Standard/Fa            | Standard/Fast/Fast+ Mode                         |            |      |     |      |      |  |  |  |

| t <sub>BUS</sub>       | Bus free time between a STOP and START condition |            | 0.5  |     |      | μs   |  |  |  |

| C <sub>BUS</sub>       | Bus line capacitive load                         |            |      |     | 150  | pF   |  |  |  |

| fscL                   | SCL clock frequency                              |            |      |     | 1000 | kHz  |  |  |  |

| tLO_SCL                | SCL low time                                     |            | 0.5  |     |      | μs   |  |  |  |

| t <sub>HI_SCL</sub>    | SCL high time                                    |            | 0.26 |     |      | μs   |  |  |  |

| t <sub>RISE</sub>      | SCL and SDA rise time.<br>Requirement for input. |            |      |     | 1000 | ns   |  |  |  |

| t <sub>FALL</sub>      | SCL and SDA fall time.<br>Requirement for input. |            |      |     | 300  | ns   |  |  |  |

| Parameter               | Description                   | Conditions | Min  | Тур | Max  | Unit |

|-------------------------|-------------------------------|------------|------|-----|------|------|

| tsetup_start            | Start condition setup time    |            | 0.26 |     |      | μs   |

| thold_start             | Start condition hold time     |            | 0.26 |     |      | μs   |

| t <sub>SETUP_STOP</sub> | Stop condition setup time     |            | 0.26 |     |      | μs   |

| t <sub>DATA</sub>       | Data valid time               |            |      |     | 0.45 | μs   |

| tdata_ack               | Data valid acknowledge time   |            |      |     | 0.45 | μs   |

| t <sub>SETUP_DATA</sub> | Data setup time               |            | 50   |     |      | ns   |

| thold_data              | Data hold time                |            | 0    |     |      | ns   |

| tspike                  | Spike suppression pulse width |            | 0    |     | 50   | ns   |

## 5.5.10 Digital I/O Characteristics

#### **Table 16: Digital I/O Electrical Characteristics**

| Parameter              | Description                    | Conditions              | Min | Тур | Max | Unit |  |  |  |

|------------------------|--------------------------------|-------------------------|-----|-----|-----|------|--|--|--|

| Electrical Performance |                                |                         |     |     |     |      |  |  |  |

| VIH_SCL_SDA            | Input high voltage, SCL, SDA   |                         | 1.2 |     |     | V    |  |  |  |

| VIL_SCL_SDA            | Input low voltage, SCL, SDA    |                         |     |     | 0.4 | V    |  |  |  |

| Vol_PG1                | PG1 output low voltage,<br>POR | I <sub>OUT</sub> = 3 mA |     |     | 0.4 | V    |  |  |  |

| V <sub>OL_PG2</sub>    | PG2 output low voltage,<br>POR | I <sub>OUT</sub> = 3 mA |     |     | 0.4 | V    |  |  |  |

| Vol_sda                | Output low voltage, SDA        | I <sub>OUT</sub> = 3 mA |     |     | 0.4 | V    |  |  |  |

| V <sub>IH_EN</sub>     | Input high voltage, CH1SEL     |                         | 1.2 |     |     | V    |  |  |  |

| VIL_EN                 | Input low voltage, CH1SEL      |                         |     |     | 0.4 | V    |  |  |  |

| tenh_deb               | EN Pin rising debounce time    |                         |     | 100 |     | ms   |  |  |  |

| tenl_deb               | EN Pin falling debounce time   |                         |     | 10  |     | μs   |  |  |  |

#### 6 Functional States

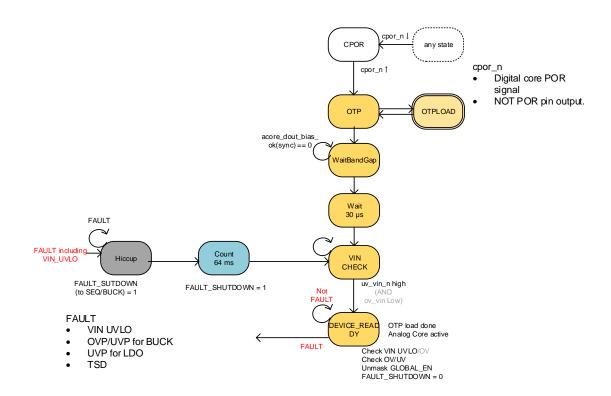

DA9080 functional states are shown in Figure 6.

Figure 6: FSM States

## 7 Sequencer

#### 7.1 Functional Description

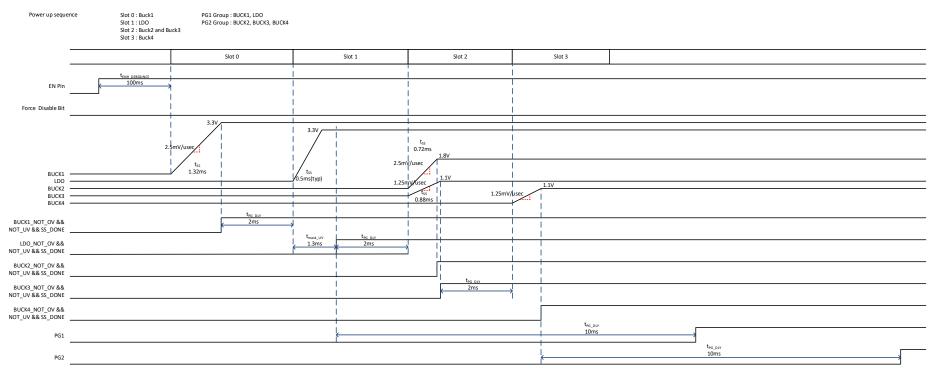

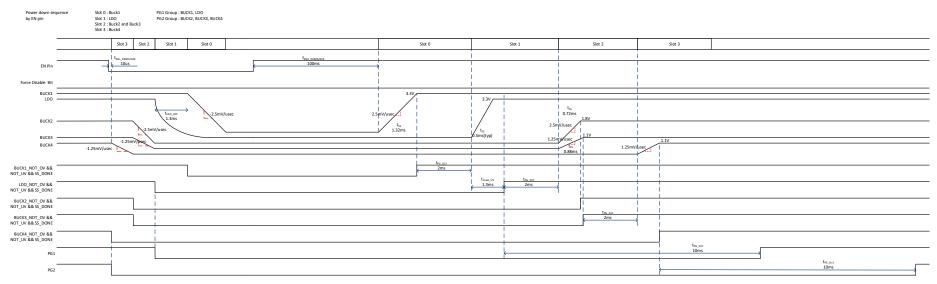

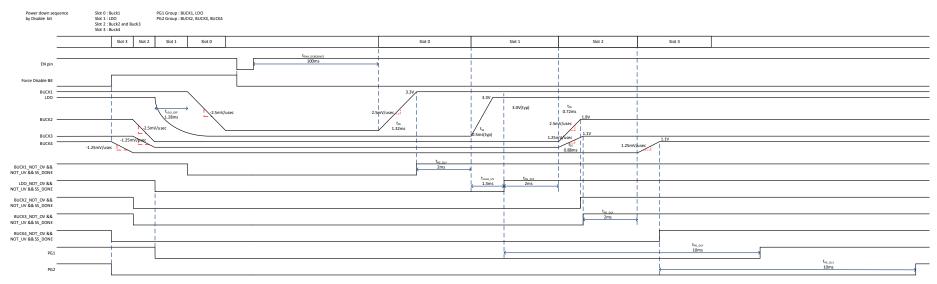

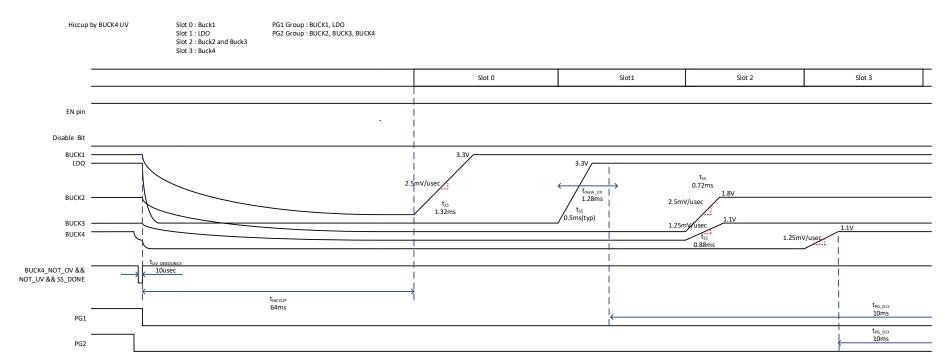

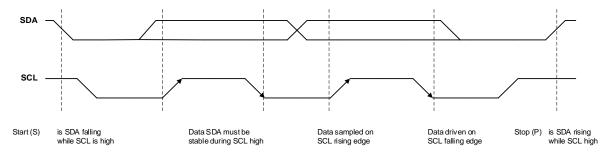

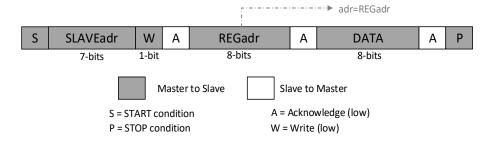

DA9080 includes a sequencer to control the power-up and power-down behavior. Any number of voltage supplies (bucks and LDO) can be grouped and assigned to a sequencer slot; for example, PVIN1 and PVIN2 may both be assigned to slot one. Four sequencer slots are provided.